9月27日,中国集成电路设计创新大会暨IC应用展(IC Show-ICDIA 2024)在无锡太湖国际博览中心落下精彩帷幕。本次大会以“应用创新、打造新生态”为主题,集中展示了AI大模型与芯片技术、IC设计、RISC-V生态、通信与射频技术等领域的技术进展与成果展示,旨在推动产业进展及未来应用。

晟联科作为国产32G/16G UCIe+112G SerDes/PCIe6.0 IP供应商受邀参展,亮相A4展馆C13展位,展出关于112G SerDes高速IP方案。同时出席【AI大模型赋能芯片设计】论坛,发表关于《SerDes+UCIe:大算力芯片C2C和D2D高速接口IP整体解决方案》主题演讲。

高速互联

晟联科112G SerDes惊艳亮相

在本次ICDIA IC Show中,晟联科重点展示了 112G SerDes IP解决方案,基于ADC/DSP的接收端架构,支持PAM4和NRZ传输。支持长距离传输:42dB@112G PAM4。低功耗,低延时,也满足了高性能计算、人工智能、通信处理等应用的数据传输使用需求。

同时,晟联科112G SerDes支持IEEE802.3bj/cd/ck、InfiniBand EDR、OIF CEI-112G-LR/MR/XSR Electrical Interfaces、SFF-TA-1028、INF-8628协议。支持线路环回和系统环回模式,BER性能优越。

112G SerDes 高速IP解决方案的展出,也收获了展会现场观众的众多关注,与晟联科现场工作人员进行了持续性交流和探讨。

左右滑动查看更多展会现场

UCIe+SerDes

赋能大算力芯片C2C和D2D高速接口IP

9月27日,【AI大模型赋能芯片设计】论坛在无锡太湖国际博览中心同期举办,晟联科高级市场总监汪成喜发表了关于《SerDes+UCIe:大算力芯片C2C和D2D高速接口IP整体解决方案》主题演讲,介绍了晟联科片内及片外的两大IP产品品类。

随着AI模型参数扩大,海量训练数据加大,对算力的需求呈现几何级数的增长。同时从单模态走向多模态发展,除了文本数据,还需要同时处理音频、图像等多种数据类型,对算力需求也有显著的增长。

算力的升级,主要体现在GPU单卡算力的飞跃和集群算力的全面增强。而算力的升级又主要通过三层架构来实现:Scale-inside、Scale-up和Scale-out。

Scale-inside:深挖单卡潜能,通过优化芯片内部结构,实现更高效的数据处理。

Scale-up:强化超节点性能,通过高速互联技术,让芯片间协同作战,提升整体超节点算力。

Scale-out:扩展集群规模,利用更多节点构建超级算力网络,应对大规模数据处理挑战。

晟联科UCIe+SerDes,赋能大芯片C2C和D2D

无论是Scale-inside、Scale-up还是Scale-out,AI x PU(加速处理器)都需要定制化的高速IP来满足其独特的算力需求。晟联科深刻理解这一点,为不同场景下的AI x PU量身打造高速互联方案。

Scale-inside:Chip内部Die-to-Die互联

在Scale-inside 层面,对IP的主要需求:Die-to-Die接口

• 同构/异构集成

• 标准化的D2D互联接口

• 高带宽

• 低延时

• 支持同构/异构下的Cache一致性NoC方案

晟联科提供了标准化、高带宽、低延时的UCIe IP解决方案,并集成了NoC,实现了芯片内部Die之间的无缝协作,极大地提升了数据处理效率。

晟联科解决方案

1、支持标准化UCIe V1.1/2.0:从IP架构设计开始,严格遵守UCIe标准,设计过程中运行UCIe Verification IP来保证遵循规范

2、高带宽:32GT/s,在私有模式下达到36GT/s

3、低延时:快至2.x ns,国产领先

4、已经做过硅验证,客户可以放心使用

5、与合作伙伴合作,提供UCIe+NoC集成优化的打包方案

•UCIe Die-to-Die Bandwidth: 128GB/s per Module

•NoC Bandwidth: 1000GB/s

•UCIe Latency: 2.x ns

•NoC Latency: 15~20ns

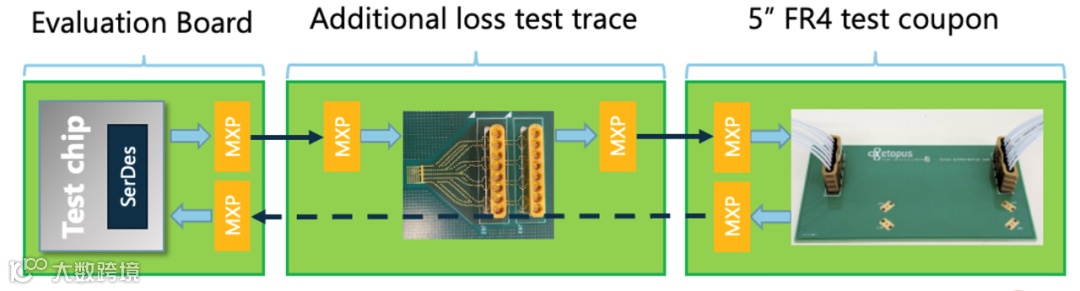

Scale-up:跨背板级别Chip2Chip SerDes/PCIe互联

对应典型的基于OAM模组的GPU多卡互联,无论是基于高速SerDes互联,还是基于PCIe的互联,晟联科都提供了高速,高插损信道下的传输,高可靠性的解决方案,为构建大规模HPC集群奠定了坚实基础。

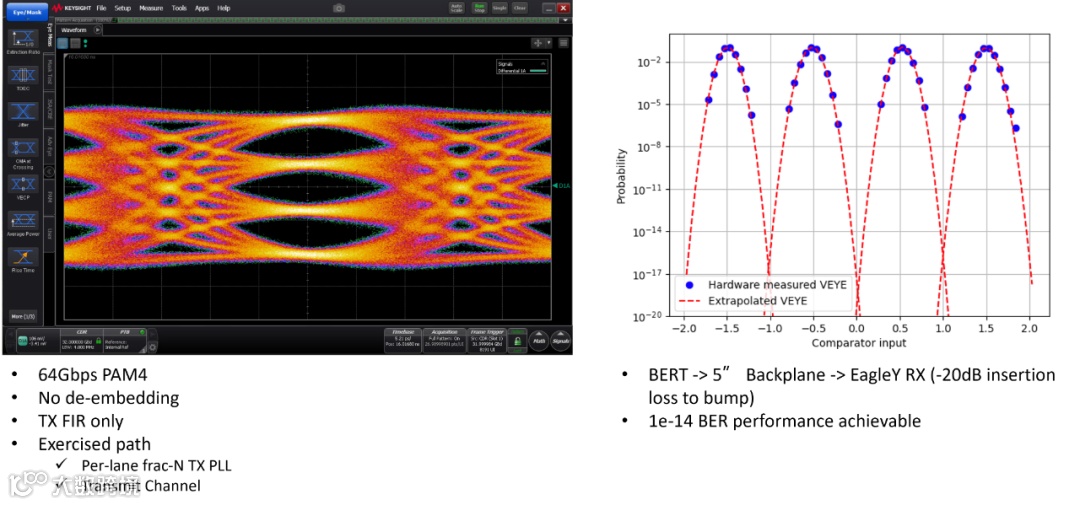

晟联科科ExtraLR 112G SerDes IP特点

1、112G SerDes

2、High Insertion Loss capability,42db@1E-6,45db@2E-4

3、Extended LR serves as external retimer

4、Superior BER performance in high insertion loss channels

5、Low power

6、Low Latency

▲ 112G SerDes Eye Test for TX

▲ 112G SerDes Extra Long Reach 40dB+

晟联科 LR PCIe IP特点

1、Fully integrated PCIe Gen1-6 and CXL solution

2、PCIe 6.0*16

3、CXL 2.0/3.0

4、Long Reach of insertion Loss capability

5、Superior BER performance in high insertion loss channels

主板内AI X PU芯片间有两种连接模式,一种是SerDes连接,另外一种则是UCIe连接。

晟联科解决方案

SerDes互联:在单板上,晟联科通过先进的SerDes技术,实现了芯片间的高速互联,确保了数据在芯片间的快速传输,高可靠性,低延时。

UCIe互联:更进一步,晟联科推出了50mm Extra LR UCIe@36GT/s解决方案,不仅延长了互联距离,还大幅提升了传输速率,为On board Chip2Chip互联树立了新标杆,一个IP实现片内和片外两种应用场景。

晟联科始终坚持技术创新作为驱动高速互联新时代的核心引擎,不仅深耕于高性能计算(HPC)、人工智能等前沿应用领域,更致力于通过持续的技术突破与解决方案优化,精准赋能客户,解决他们在数据传输速度、计算效率、系统稳定性及成本效益等方面的关键利益点,从而推动产业升级,加速客户价值实现。