插播:天科合达、天岳先进、同光股份、烁科晶体、泰坦未来、芯聚能、三安半导体、安海半导体、华卓精科、快克芯装备、合盛新材料、京航特碳、恒普技术、奥亿达新材料、凌锐半导体、中电化合物、东尼电子、西格玛、铭扬半导体等已确认参编《2025碳化硅衬底与外延产业调研白皮书》及《2025碳化硅器件与模块产业调研白皮》,参编咨询请联系许若冰(hangjiashuo999)。

瞻芯电子&浙江大学:

发表10kV SiC MOSFET研发成果

6月4日,瞻芯电子在官微透露,他们在第37届国际功率半导体器件和集成电路研讨会上,与浙江大学以大会全体报告的形式联合发表了10kV等级SiC MOSFET的最新研究成果,受到了各界广泛关注。

据悉,10kV等级SiC MOSFET器件在下一代智能电网、高压大容量功率变换系统等领域有广阔的应用场景。但受困于材料及工艺成熟度问题,早期的相关工作多局限于芯片功能展示,芯片面积普遍较小,通流能力较差。如何进一步增加芯片面积,并保持良好的芯片制造良率和可制造性,一直是学术界和产业界面临的巨大挑战。

图3:本次成果与历史成果对比(黄色虚线为SiC材料理论极限)

加入碳化硅大佬群,请加微信:hangjiashuo999

加入碳化硅大佬群,请加微信:hangjiashuo999

公布2项SiC器件新技术

6月9日,东芝电子元件及存储装置株式会社在官网透露,他们已开发出创新技术,一方面可以显著降低沟槽栅SiC MOSFET的损耗,同时增强UIS(非钳位电感开关)的耐用性。另一方面,他们还开发了SiC半超结肖特基势垒二极管 (SJ-SBD),可抑制高温下导通电阻的上升。

东芝电子表示,沟槽栅SiC MOSFET必须保护栅极氧化层免受高电场的影响,但UIS耐用性与电场保护结构接地电阻之间的关系尚不清楚,因此难以同时实现高栅极氧化层可靠性和低导通电阻。此外,尽管SiC SBD可以在比传统Si SBD更高的温度下工作,但它们必须能够承受高温下电阻的增加,这会导致导通电阻更高。

所以,东芝电子开发了两项关键技术来解决这些问题:

提高SiC Trench MOSFET UIS耐久性的技术

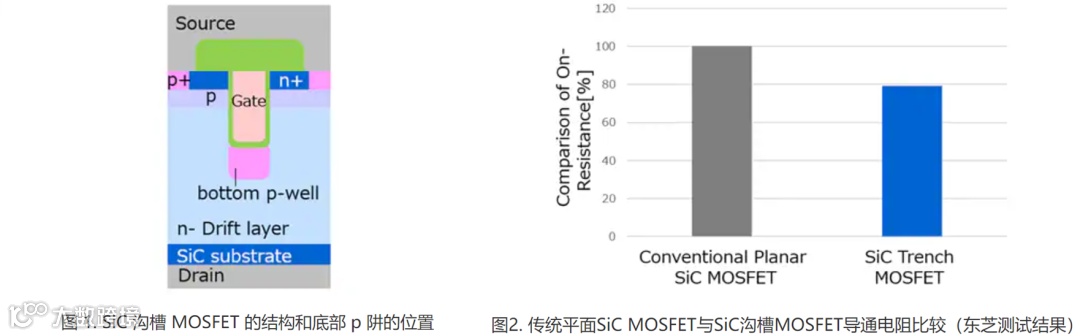

东芝电子确认,在沟槽栅SiC MOSFET的沟槽内形成一层名为“底部p阱”的保护层(图1),并适当降低“底部p阱”的接地电阻,可以提高UIS的耐久性。这澄清了此前UIS耐久性与电场保护结构接地电阻之间不确定的关系。

通过该技术,东芝电子试制的沟槽栅SiC MOSFET与传统的平面型SiC MOSFET相比,导通电阻降低了约20%(图2)。

-

SiC SJ-SBD特性的改善

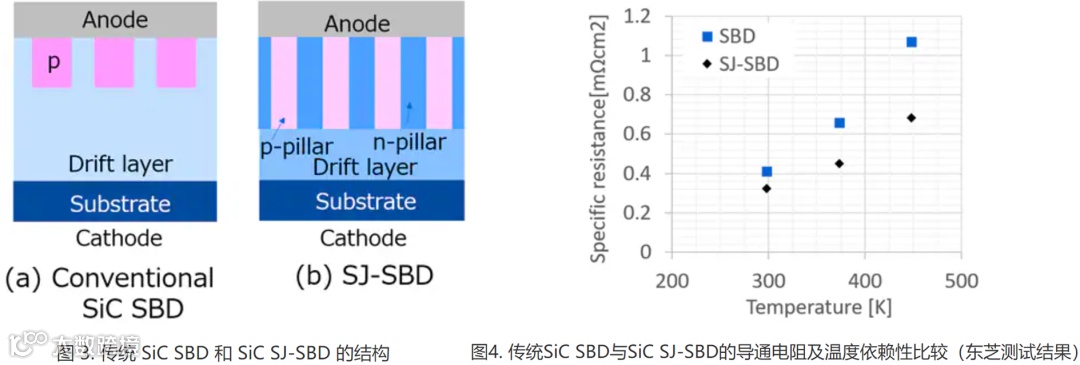

东芝还开发了 SiC SJ-SBD,通过在漂移层中放置柱状结构来降低电阻,从而抑制高温下的电阻增加(图 3 (b))。通过比较传统 SiC SBD(图 3 (a))和 SiC SJ-SBD 在不同温度下的导通电阻变化,东芝证实了 SiC SJ-SBD 的导通电阻较低,尤其是在高温下(图 4)。

这是由于 SJ 结构实现了平坦的电场分布并降低了导通电阻。与传统 SiC SBD 相比,东芝开发的 650V SiC SJ-SBD 在 175°C(448.15K)的高温下导通电阻降低了约 35%。

东芝电子进一步透露,这两项技术进一步降低了沟槽栅SiC MOSFET和SiC SBD的损耗,提高了器件的可靠性和效率,可用于未来的高效功率转换应用,他们的目标是进一步改进这些技术,并尽早实现实际应用。

本文发自【行家说三代半】,专注第三代半导体(碳化硅和氮化镓)行业观察。