本期是平台君和您分享的第121期内容

JESD204通信标准是由JEDEC国际协会在2006年发布的,用于数据转换器(ADC和DAC)与逻辑器件(如FPGA)之间数据传输的高速串行接口标准。经过10多年的发展,最新的JESD标准已经发展到JESD204C,传输速率已经达到32Gbps。

PART 01

为什么会出现JESD通信标准?

这个问题问得好,每一项新技术的出现,肯定是为了解决某个问题,也就说有用。没有人会发明一些没用的东西,不好意思 ,手工耿除外。

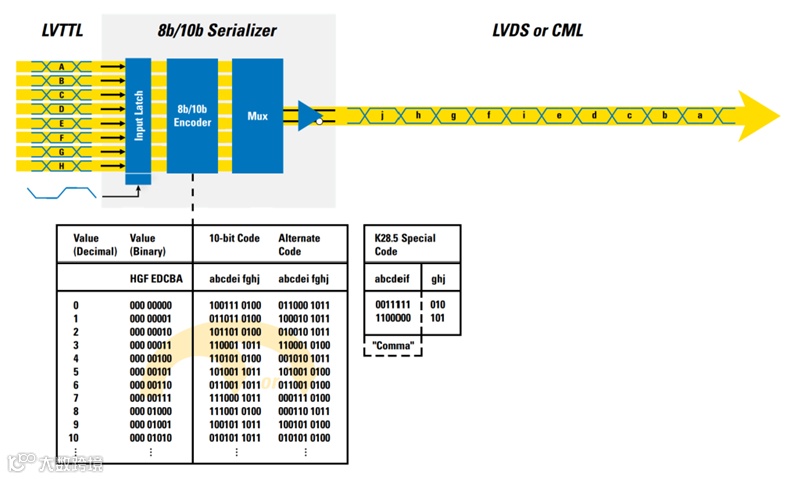

下图为8b/10b的串化示例。

下图为A/D应用中,经过8b/10b串化为串行数据,通过发送器发送给数据处理器后,解串为并行数据的实例。

随着现代电子系统的发展,数据转换器(如ADC和DAC)的采样率和分辨率不断提高,这导致了数据量的急剧增加。传统的并行接口在高速传输这些大数据量时遇到了瓶颈,例如传输线数量多、信号间干扰大、传输距离受限等问题。JESD标准采用高速串行传输方式,能有效解决这些问题,实现了更高的数据传输速率,像JESD204B标准下传输速率可达12.5Gbps,满足了高速数据传输的需求——人类对速度的追求从来没有放弃过。

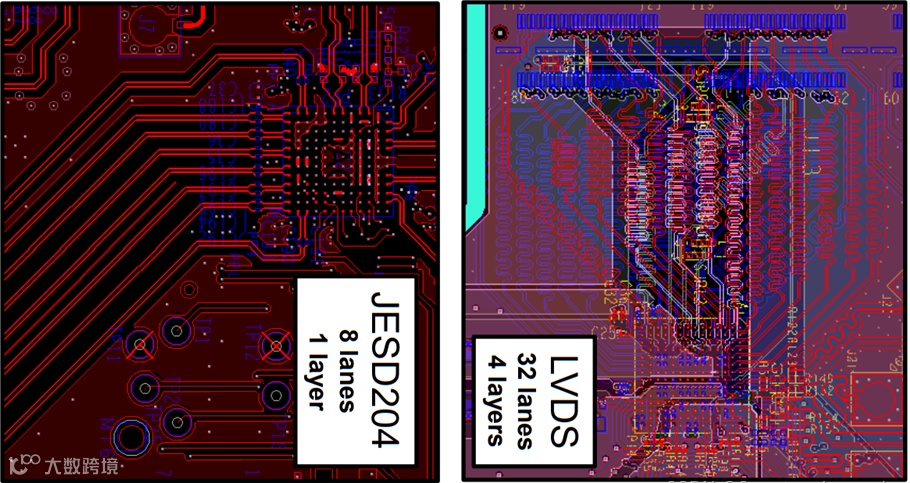

举个例子,在JESD204接口出现以前,数模转换器的数字接口绝大多数是差分LVDS的接口,这就造成了PCB布线的困难。当PCB的密度很大的时候就需要增加板层从而造成印制板的成本上升。而JESD204接口是串行接口,能有效减少数据输出的差分对,一方面能最大限度简化布线——人类对偷懒的追求从来没有放弃过。另一方面而节省成本——人类对低成本的追求从来没有放弃过。

如下图为同样的DAC,使用LVDS接口和J204B接口下的设计对比。

下图为两种接口的PCB走线比对,显然,JESD204明显简化很多。

另外,JESD标准使得不同厂商生产的数据转换器和逻辑器件(如FPGA)之间能够更方便地进行通信和集成。只要设备都遵循JESD标准,就可以更容易地构建复杂的混合信号系统,如在通信基站中集成ADC、DAC和FPGA来实现信号的采集和处理。

平台君想起小时候看到父辈们的各种手机,充电接口都不一样。诺基亚的充电器,没法给摩托罗拉手机充电;三星的充电器没法给诺基亚充电,摩托罗拉的手机没法给西门子手机充电,家里如果有不同品牌的手机,需要每个品牌都用一个充电器。直到后来Type C这个统一接口的出现,终于出门只要一根数据线就够了。

当然,平台君也发现,虽然Type C统一了,但现在各个手机厂商还是对别家数据线做了限制。平台君的小伙伴们测试过,华为的快充线,充OV手机时候,充电速度很慢,同样地,OV快充头和快充线充华为手机时候,充电速度也很慢。

有点扯远了,言归正传,我们一起来看下JESD204的发展历程。

PART 02

JESD204通信标准发展历程

JESD204:2006年4月问世,当时ADC或DAC的速率和分辨率要求不高,此标准只考虑了一个通道和一个链路,传输速率达3.125Gbps,发送端与接收端共用一个系统时钟。

JESD204A:2008年4月发布,支持多链路和多通道串行数据传输,添加了转换器的多重对准能力,最高传输速率仍为3.125Gbps。

JESD204B:2011年8月发布,可支持单个转换器的内部同步和多个转换器之间的同步,数据传输速率可达12.5Gbps,且速率有不同等级,还提供了子类0、子类1、子类2三种传输模式。

JESD204C:2017年底发布,数据传输速率可达32Gbps。64b/66b编码使超高带宽应用,能以最小的开销来提高系统效率。JESD204C的改进对5G通信、 B5G、6G通信系统、气象雷达和电子对抗、先进的仪器仪表和其他应用都大有裨益。

几种标准的参数对比

PART 03

JESD204技术特点和优势

高速传输能力

- JESD204采用CML技术传输信号,其B修订版支持高达12.5Gbps的串行数据速率,最新的C版本更是可支持高达32Gbps的数据速率,能够满足高速ADC、DAC转换器等对高数据传输率的需求。

- 作为串行接口,相比传统的并行接口,JESD204大大减少了引脚数量,降低了布线复杂度,使电路板设计更加容易,有助于实现更小的封装尺寸和更低的系统成本,尤其适用于高密度电路板设计。

- 采用嵌入式时钟和8b/10b编码,无需额外的时钟线路,避免了高速率下数据与时钟信号对齐的复杂性,同时确保数据有足够频繁的信号跳变,利于接收端时钟恢复,并且可实现直流平衡,提升链路的噪声和抖动性能。

- JESD204B提供了子类0、子类1、子类2三种不同的传输模式,可支持单个转换器的内部同步和多个转换器之间的同步,其中子类1还支持确定的延时,能更好地满足不同应用场景对同步和延时的要求。

- 该标准已被众多转换器供应商、用户以及FPGA制造商所采纳,具有良好的兼容性和可扩展性,能够方便地与其他高速串行接口标准进行桥接和集成,如PCI-E、SATA、SAS等。

- 采用差分信号传输,具备较好的抗干扰性,在高速数据传输过程中能够有效降低噪声和串扰的影响,保证数据传输的准确性和可靠性。

PART 04

哪些芯片采用了JESD204通信技术

根据平台君的不完全统计,采用了JESD204技术的芯片大多数为ADC、DAC和FPGA,部分型号如下:

芯片型号 |

支持的JESD204技术 |

AD9144 |

Flexible 8-lane JESD204B interface Support quad or dual DAC mode at 2.8 GSPS |

AD9154 |

JESD204B Subclass 1 |

AD9164 |

eight lanes JESD204B |

AD9174 |

8-lane, 15.4 Gbps JESD204B |

AD9208 |

JESD204B (Subclass 1) coded serial digital outputs Support for lane rates up to 16 Gbps per lane |

AD9213 |

16-lane JESD204B output (up to 16 Gbps line rate) |

AD9371 |

JESD204B interface supports lane rates up to 6144 Mbps |

AD9081 |

DAC Maximum data rate up to 12 GSPS using JESD204C ADC Maximum data rate up to 4 GSPS using JESD204C SERDES JESD204B/JESD204C interface, 16 lanes up to 24.75 Gbps |

AD9084 |

JESD204B/JESD204C:20 Gbps/32.5 Gbps |

Xilinx Virtex UltraScale+ |

JESD204A/204B,3.125–12.5 Gbos |

Achronix Speedster7t FPGA |

JESD204C |

Intel Agilex®7 E-Tile devices |

JESD204C |

好啦,今天的分享就到这里,喜欢的话,记得点赞和关注哦。平台君还年轻,能力和认知有限,难免会有疏漏和错误,如果有技术大牛,欢迎批评和指正。

关于IPBrain平台

IPBrain集成电路大数据平台归属北京芯愿景公司旗下。IPBrain平台为半导体行业客户提供先进芯片技术资讯、专利资讯、市场动态等信息。平台可以分析的最先进制程已达到3纳米,单个项目最大规模达超过100亿个晶体管,最大金属层数达到20层,目前平台已积累的报告有13000+。

欢迎关注IPBrain平台公众号及网站:https://www.ipbrain.com.cn,及时掌握技术动态和市场资讯,精准研发不走弯路,更快实现产品成

★往期精彩推荐★

2024-11-27

2024-11-26

2024-11-26

2024-11-25

2024-11-25

2024-11-25

2024-11-22

2024-11-21

2024-11-20

2024-11-19