本文转载自电科星拓,转载文章仅供学习和研究使用。

DDR技术简介

DDR内存频率与CPU外频同步,且允许在时钟脉冲上升沿和下降沿传输数据,大幅提升了数据传输效率。

64bit的数据位宽与当时CPU的总线一致,只需要一根内存就能让电脑正常工作了,这降低了采购内存的成本。

DIMM的组成与应用

-

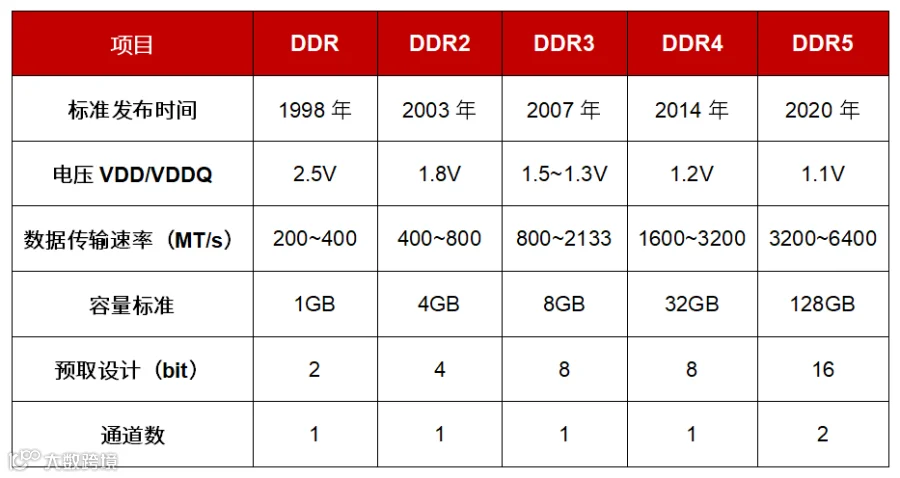

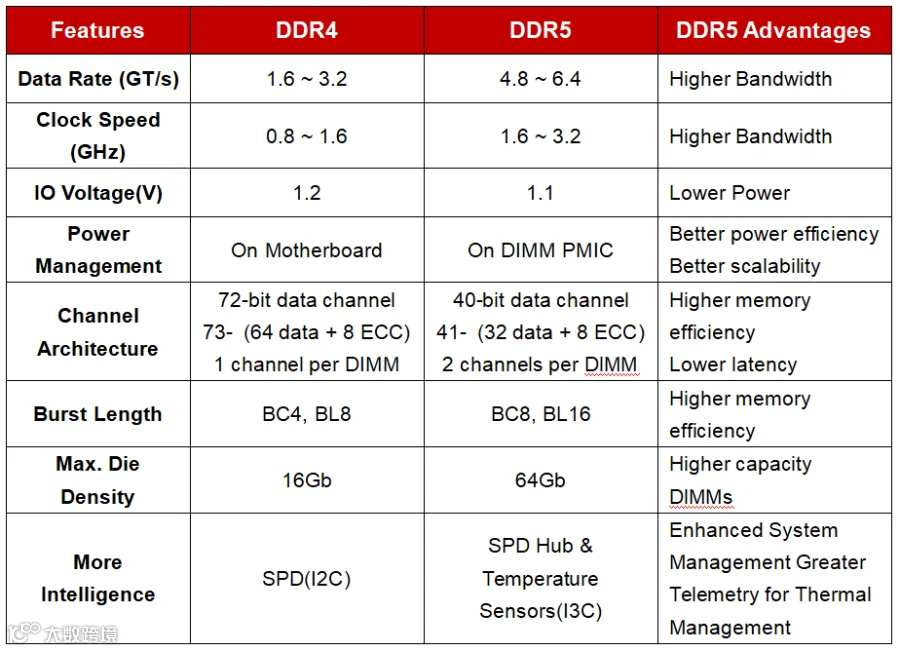

DDR5内存速率最终将达到6.4 Gbps,2倍于DDR4。 -

DDR5中集成了DFE等新功能,从而实现了更高的IO速度。

-

DIMM内置12V电源管理IC(PMIC)。DDR5 DIMM电源管理从主板转移到DIMM内,生成1.1V VDD电源,实现更好的负载管理,有益于信号完整性和噪声控制。 -

DDR5通道架构更新。DDR4 DIMM具有72位总线,由64个数据位+8个ECC位组成。DDR5每个DIMM有两个通道,每个通道均为40位宽:32个数据位和8个ECC位。尽管总数据宽度都是64位,但具有两个较小的独立通道可提高内存访问效率。 -

DDR5集成了细粒度存储库刷新功能。允许某些存储库在使用中的同时进行刷新,进一步降低等待时间。

-

借助DDR5缓冲芯片DIMM,服务器或系统设计人员可以在单芯片封装(SDP)中使用多达64Gb DRAM的密度,而DDR4 SDP中最大仅可容纳16Gb DRAM。 -

颗粒容量增加带来DIMM容量的增加。举个例子,DDR4 DIMM在使用SDP的情况下最大容量为64 GB,而DDR5可以做到256 GB。 -

DDR5支持片上ECC,错误透明模式,封装后修复以及读和写CRC模式等功能,以支持更大容量的DRAM。

-

DDR5的Burst Length(BL)扩展到16,以增加突发有效负载。允许单个突发访问64字节的数据,显著提高了并发性,提高了内存效率。

DDR5技术的应用前景

往期推荐

|

|||

|

|||

|

牛芯半导体(深圳)有限公司(简称“牛芯半导体”)成立于2020年,聚焦接口IP的开发和授权,并提供相关整体解决方案,致力成为全球领先的IP供应商。

基于自主可控的核心技术,牛芯半导体在主流先进工艺布局SerDes、DDR等中高端接口IP,产品广泛应用于消费电子、网络通信、数据存储、人工智能、汽车电子、医疗电子等领域。

未来,牛芯半导体持续响应IP国产化需求,适应不断演进的接口技术和日益拓展的接口互联场景,赋能数智时代下的千行百业。