本文转载自极术社区,转载文章仅供学习和研究使用。

什么是DDR?

DDR实现的复杂性

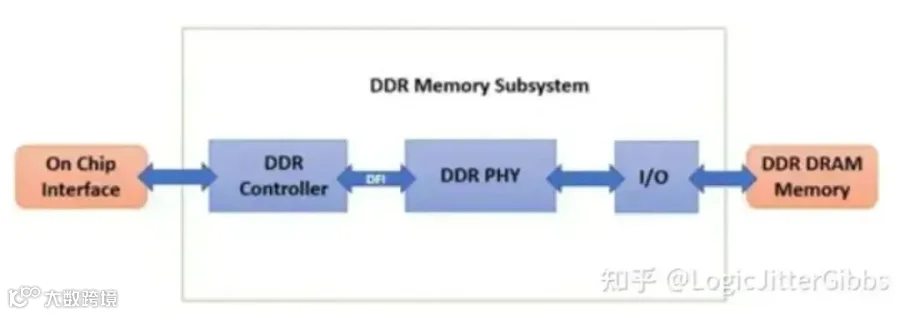

深亚微米SoC设计集成了在超过1GHz时钟速率下运行的DDR内存子系统,高速时钟导致读写时序裕量以皮秒为计。这使设计师担心DDR内存系统的时序裕量由于工艺产生静态变化,以及其由于系统运行条件(如温度和电压)波动引起的动态变化,导致系统无法工作。

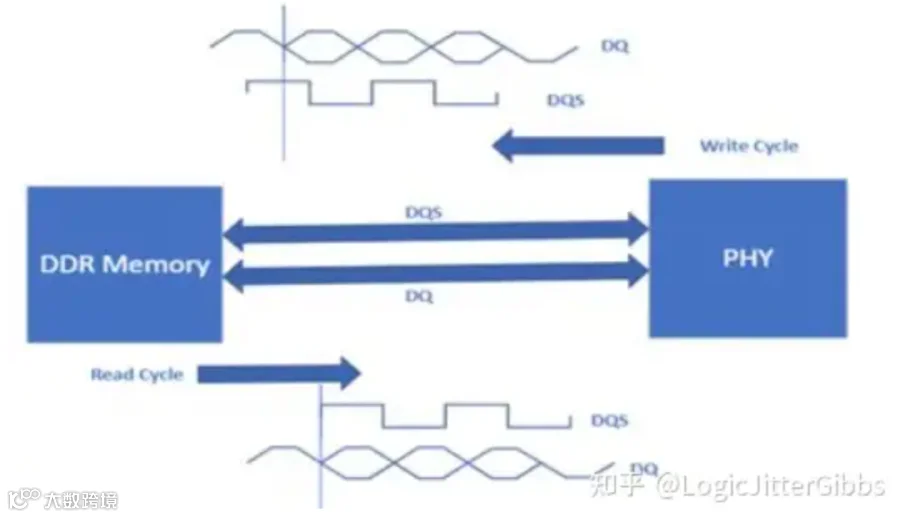

1. DDR I/O时序要求更严格,因为数据在时钟的两个边缘传输,所以有效数据持续时间只有半个周期。DDR中的逻辑通常涉及正边沿触发的触发器、负边沿触发的触发器甚至锁存器。

2. 随着数据速率的增加,与内存接口的时序和信号完整性相关的复杂性变得越来越困难。

3. 对于DDR信号,随着频率的增加,单个比特的传输时间减少,导致由传输时间均分得到的Setup和Hold时序预算也随之减少。

DDR IP硬化

-

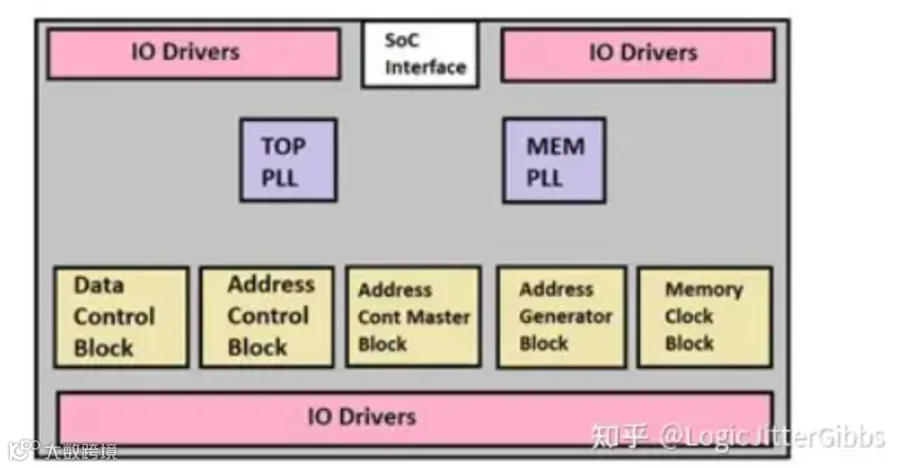

数据控制模块:它控制数据读写操作。它将DQ、以及相关的DM和DQS 信号连接到DRAM。可以复制多个数据模块,提供需要的DRAM接口数据宽度。 -

地址控制模块:它生成DRAM控制信号,片选(CS)、地址选择(AS)和其他控制信号的数量可以根据需求配置。 -

内存时钟模块:它为DRAM提供DDR时钟。 -

地址控制主模块:是所有地址控制模块的主控制模块。 -

加法器生成模块:用于生成需要通过加法计算得到的DRAM地址。(译注:加法器不是必须的,实际实现中一般尽量通过移位等运算生成DRAM地址) -

PLL:DDR顶层模块中包括两个PLL,一个PLL生成PHY所需要的工作时钟(译注:PHY时钟频率可能和DDR IO时钟相同,或者是DDR IO时钟的二分之一或者两倍),另一个PLL用于内存时钟模块生成提供给DRAM的DDR IO时钟。

布局规划指南

-

IO驱动器的放置顺序应与数据和地址模块的引脚顺序相匹配。这样我们可以减少走线交叉并更好地对齐信号边沿,有助于满足skew需求。 -

最好通过脚本来确保从模块到IO的信号使用相同的缓冲模型、高层金属层、NDR进行缓冲。 -

时钟引脚应该放置在Floorplan的中心,以平衡DDR模块顶层两侧的skew。来自数据和地址模块的关键信号在放置时需要特别考量。 -

Bump放置需要特别注意,以减少电阻并满足PERC和ESD要求。 -

由于DDR时序约束非常复杂,最大延迟和偏斜相关约束可能不会包含在PD使用的SDC中。(译注:这里表达的意思可能是,最大延迟和skew相关约束不会放在Synth,CTS以及PR的SDC中,因为他们可能引入其他问题。而是由前端在后端实现完成后再进行Special check)。相位检测逻辑、PLL逻辑、时钟MUX需要在布局规划期间手动规划位置,因为工具可能没法进行准确的放置。在DDR hardening期间如果没有遵循这些指南,可能会导致严重的Skew不满足。 -

DDR数据传输速率、DDR协议、封装类型、P/G比率、封装去耦电容和PCB去耦电容容值,决定了DDR模块整体的去耦要求。必须预先放置IO驱动器的去耦电容。(译注:因为去耦电容有指定的放置位置,一般位于Die边缘和DDR模块逻辑之间。)

放置指南

-

DDR连接SoC核心逻辑的端口,需要通过Magnet placement放到尽可能靠近其SoC逻辑的端口处,以减少数据延迟。 -

数据和时钟偏斜信号、时钟Mux和相位检测逻辑、IO驱动器及其驱动逻辑在优化期间应保持不变,并且应手动放置。

顶层时钟和偏斜平衡指南

-

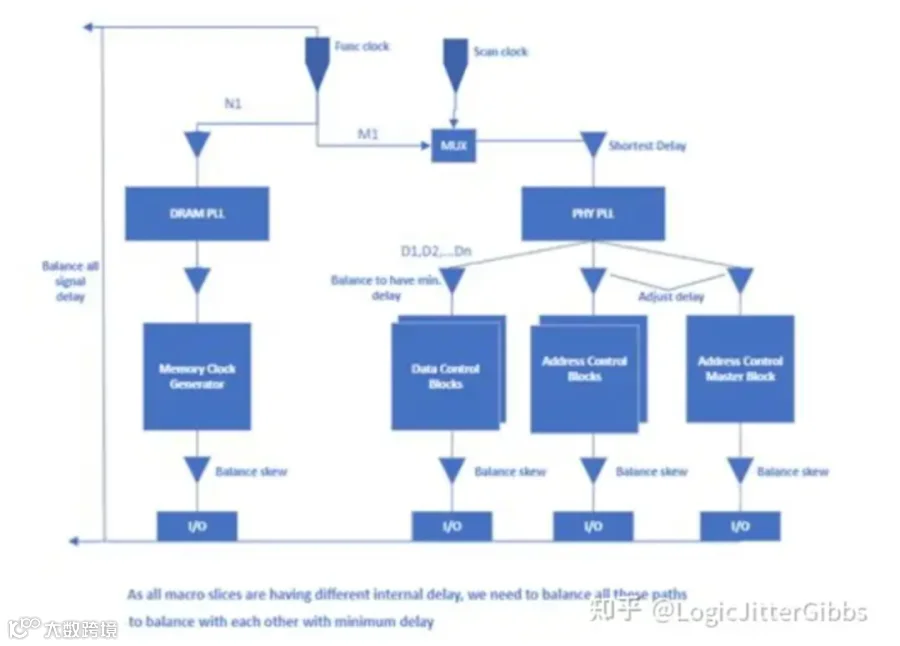

保持DDR IO时钟与DDR PHY时钟之间的相位差异尽可能小。 -

保证在DDR器件上的数据信号、控制信号和地址信号的Setup和Hold时序符合要求。 -

保持所有时钟的占空比在整个时钟路径上不会出现变化,检查所有时钟路径上的占空比,以防止畸变。 -

从时钟端口到模块内部的输入端口采样触发器和输出端口驱动触发器的信号应彼此平衡。 -

在硬化DDR顶层下的子模块时,尽可能确保他们的触发器时钟的插入延迟(insertion delay)尽可能小。 -

在硬化模块之后,在顶层构建CTS(时钟数)时,我们需要考虑子模块内的时钟网络延迟,并尝试使整个DDR顶层下每个触发器的偏斜值或多或少保持一致。 -

在构建时钟树时,我们从功能时钟或者扫描时钟输入端口开始,先构建公共时钟到第一级时钟扇出引脚的时钟树,然后再从时钟逻辑输出构建时钟树到所有模块。 -

为了避免任何额外的时钟延迟,我们将PHY时钟PLL放置在顶层的中心区域,并将DDR IO时钟PLL放置在靠近DRAM时钟生成模块的位置。此外,保证每个PLL相关的时钟逻辑放置在其附近。 -

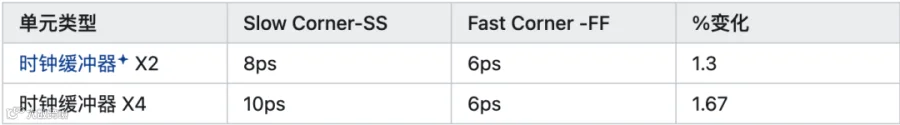

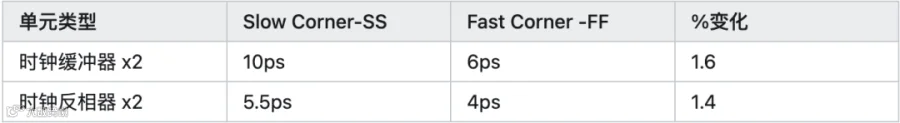

由于DDR模块的数据频率要求很高,我们使用了具有对称上升和下降延迟的高驱动器反相器,手动构建了高层金属层的时钟树,应用了NDR,并在需要的地方使用了屏蔽(shielding)以避免串扰(Cross talk)。 -

注意以下对于从子模块到IO信号的偏斜要求:

1. 以几乎相同的长度和电阻布线,以实现相等的延迟。宏单元到IO的距离应最小。

2. 宏单元到IO的距离应最小。

3. 使用NDR、屏蔽、高层金属层进行布线。

4. 在这些信号路径上添加相等数量的缓冲器。

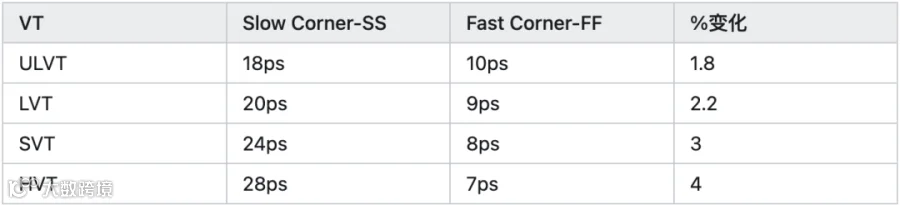

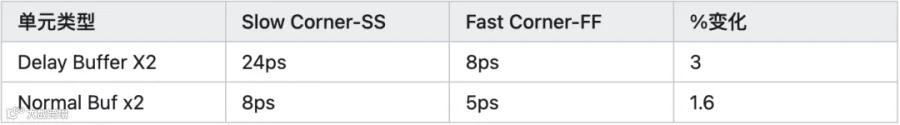

偏斜相关标准库单元的建模

-

解决放置和布线的一致性问题。 -

确保Master和Slave模块行为的一致性。 -

实现各个宏模块间的延迟一致性。

IR和EM收敛

参考文献:

1. 实用设计和可配置 DDR2 PHY 的实现 By Lior Amarilio, ChipX

2. http://www.latticesemi.com/view_document?document_id=9187

3. http://citeseerx.ist.psu.edu/viewdoc/download;jsessionid=3A728921C170B999834F9E5760C8B639?doi=10.1.1.84.4088&rep=rep1&type=pdf

4. http://www.ijeert.org/pdf/v2-i6/8.pdf

5. https://www.design-reuse.com/articles/20146/ddr-sdram-controller-ip.html

6. https://www.synopsys.com/designware-ip/technical-bulletin/ddr-hardening-demystified.html

往期推荐

|

|||

|

|||

|

牛芯半导体(深圳)有限公司(简称“牛芯半导体”)成立于2020年,聚焦接口IP的开发和授权,并提供相关整体解决方案,致力成为全球领先的IP供应商。

基于自主可控的核心技术,牛芯半导体在主流先进工艺布局SerDes、DDR等中高端接口IP,产品广泛应用于消费电子、网络通信、数据存储、人工智能、汽车电子、医疗电子等领域。

未来,牛芯半导体持续响应IP国产化需求,适应不断演进的接口技术和日益拓展的接口互联场景,赋能数智时代下的千行百业。