上一期,我们和大家一起探讨了DDR技术的发展和应用前景。本期,我们将重点对DDR5技术的重要应用领域之一——RCD,探究和交流RCD的发展与应用。

RCD全称为寄存器时钟驱动器(Registering Clock Driver)。RCD可用于寄存器双列直插内存模组(RDIMM)和减载双列直插内存模组(LRDIMM),目前最高支持6400MT/s速率。该芯片主要对DDR的地址和控制信号进行信号加强驱动,该芯片采用双通道内存架构,更为节能。为数据密集型应用如高性能计算、人工智能等提供更高容量、更低功耗的内存解决方案。该驱动器需要符合JEDEC DDR5 RCD相关标准。

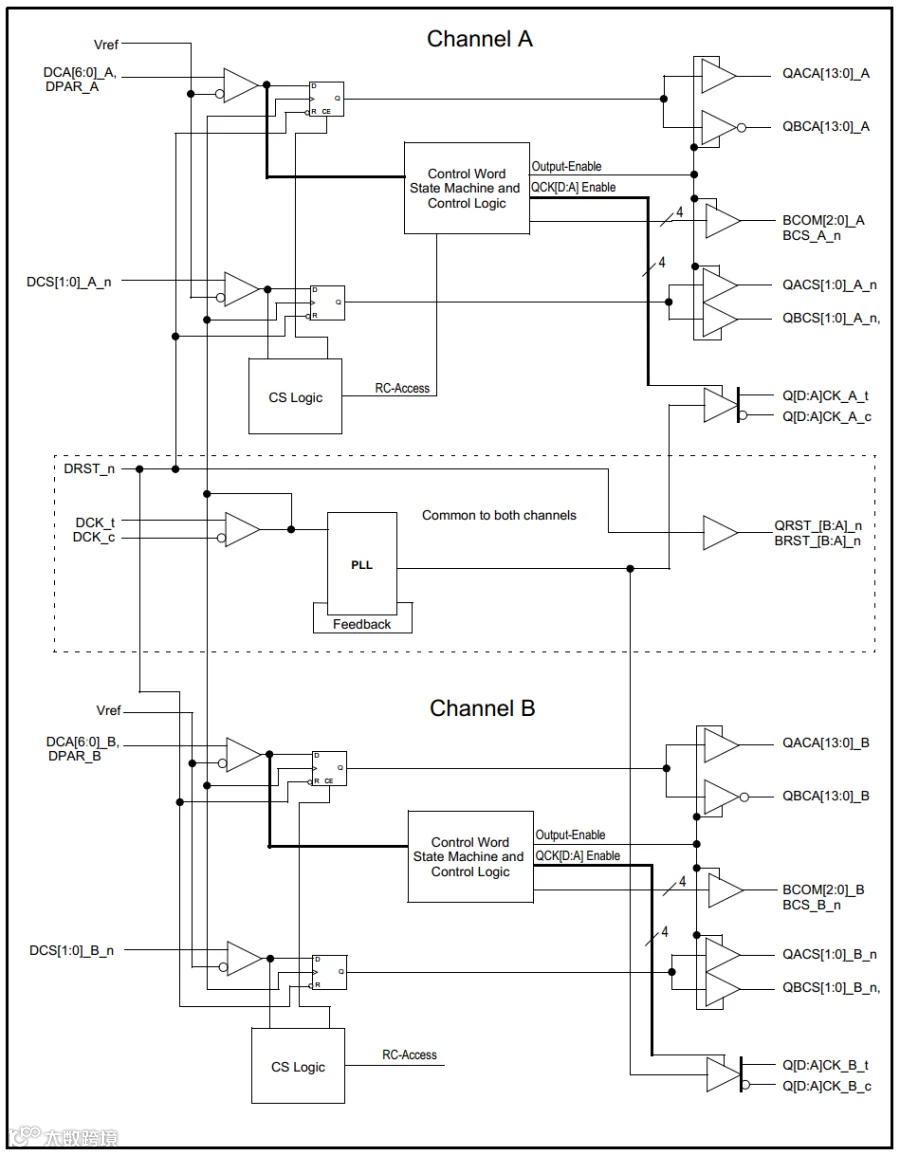

JEDEC规定RCD的芯片架构图(RCD01-RCD03)如下:

RCD芯片主要由全芯片共用的时钟复位通路、两个独立运行的通道、以及Sideband总线组成。

输入包括一对差分时钟以及一个复位信号。输出包括对每个通道输出4对用于DRAM的差分时钟和1对用于DB的差分时钟,以及对DRAM和DB的各1对复位。

输入包括7 bit的CA信号,1 bit的校验信号(PAR)和2 bit的片选信号(CS)。输出给DRAM的包括两组14 bit的CA信号和4 bit的CS信号。输出给DB的包括3 bit的BCOM信号和1 bit的BCS信号。通道内的逻辑包括寄存输入、一系列配置寄存器用于控制芯片的工作模式(部分配置寄存器只能通过通道A访问),以及解析地址命令以实现一系列动作(如判断校验、进入节电模式、或控制DB等)。

支持I2C和I3C模式,用于带外访问控制上述配置寄存器。

RCD正常工作下,可以有不同的工作模式:普通工作模式、Power Down模式、Pass Through模式、VHost模式和Transparent模式(RCD04/05不支持)。

64bit的数据位宽与当时CPU的总线一致,只需要一根内存就能让电脑正常工作了,这降低了采购内存的成本。

每个通道输入:7 bit CA,1 bit校验,2个片选CS;

每个通道输出:两份SDR的14 bit CA,两份(共4个)CS。

对于双周期命令,第一个周期DCS为0,第二周期保持为0,表示取消命令;当RW01[1]=0,QCA被屏蔽(置高)。否则在主机发送命令时将DCA传递到QCA,没有命令时QCA置高;当单周期命令或双周期命令的第一个周期出现校验错误,DCS不被传递到QCS,QCS保持为1;当双周期命令的第二个周期出现校验错误,QCS在第二个周期保持为0;当RW01[1]=0,QCS被屏蔽(置高)。

-

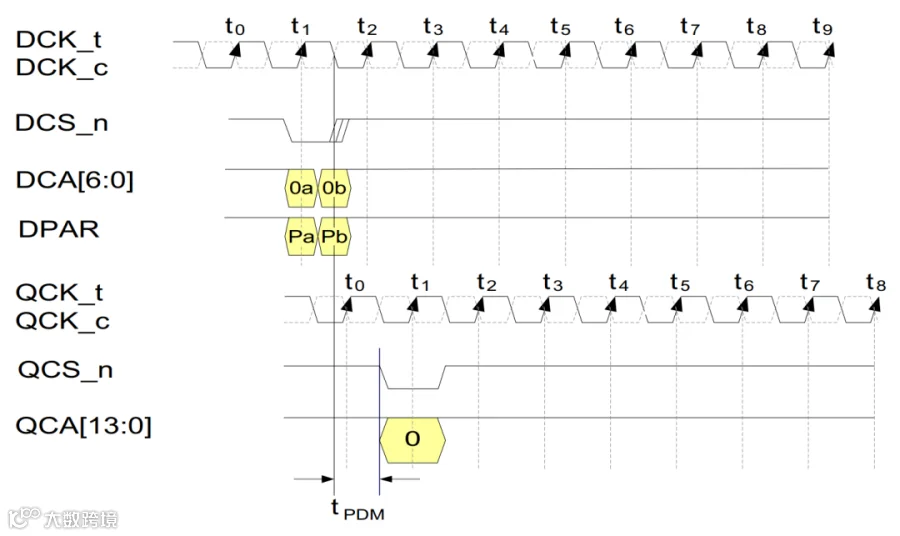

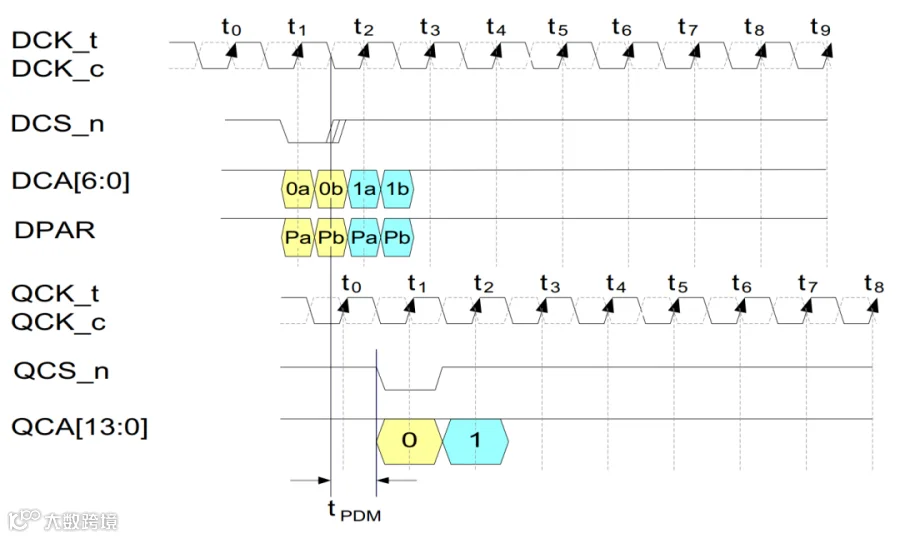

RCD对于DCA支持两种速率模式,DDR和SDR。

-

-

RCD对于QCA和QCS固定为SDR速率。两个7 bit DCA输入拼接成14 bit QCA输出。

DDR模式下,时序宽度会变为2倍。允许更多的setup time或者hold time。时序图如下(分别为更多setup和更多hold):

DDR和SDR的模式选择在初始化的tSTAB01和tSTAB02之间,或者在退出Self Refresh w/Clock Stop后的tSTAB01后。正常运行时不允许切换。如下图所示:

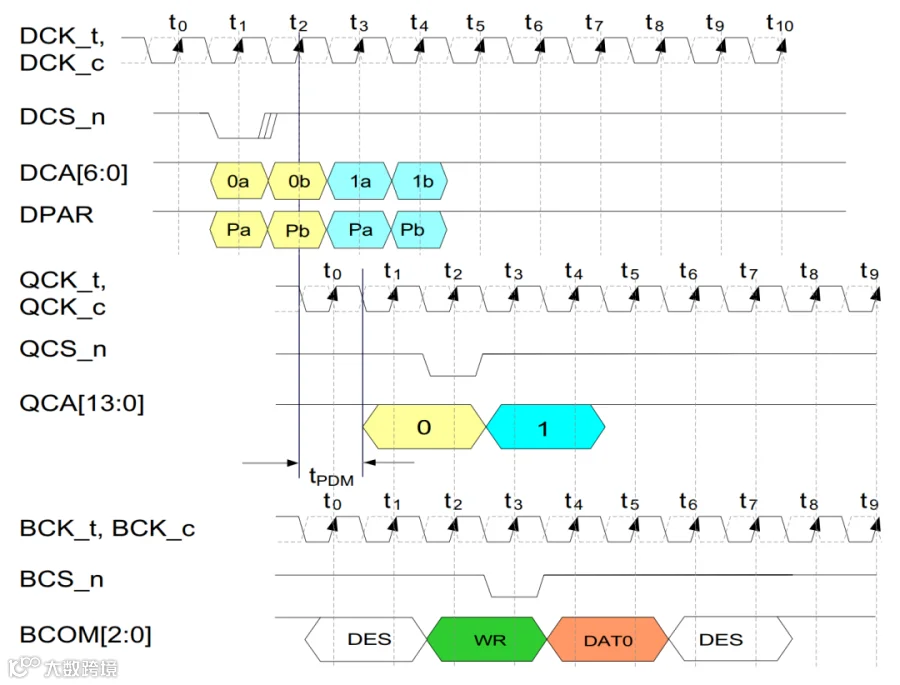

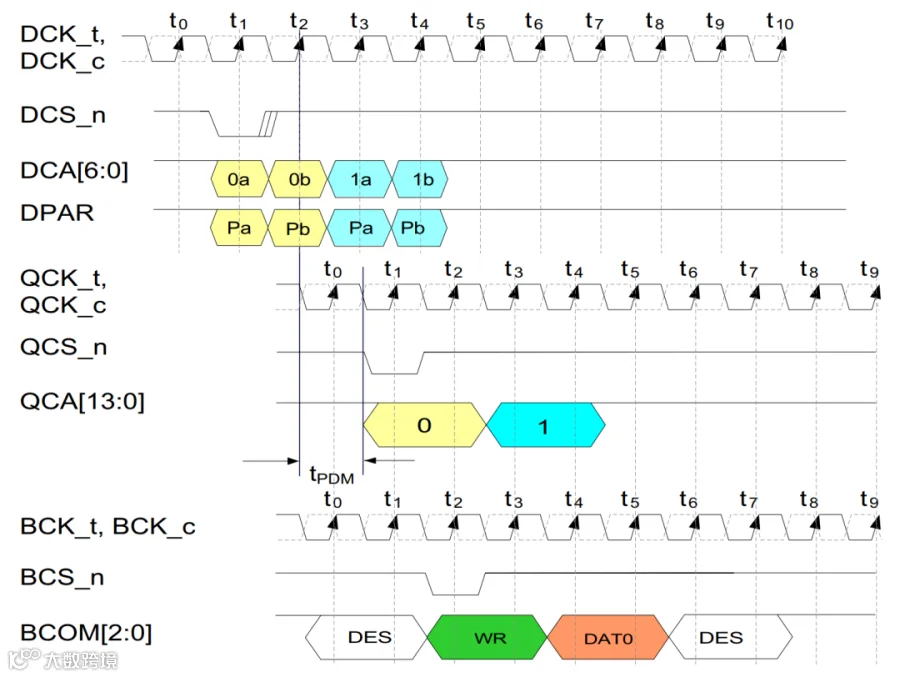

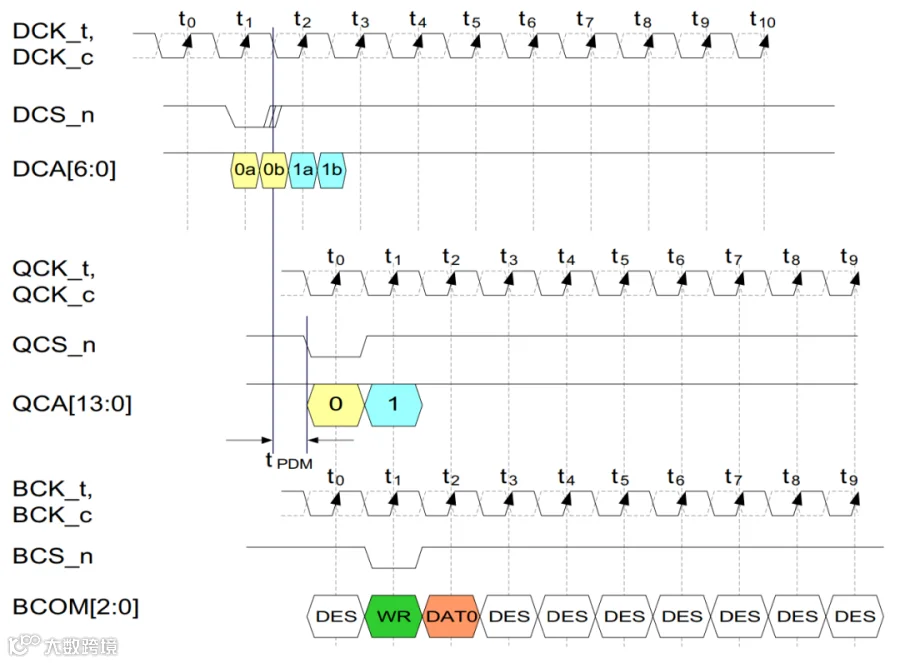

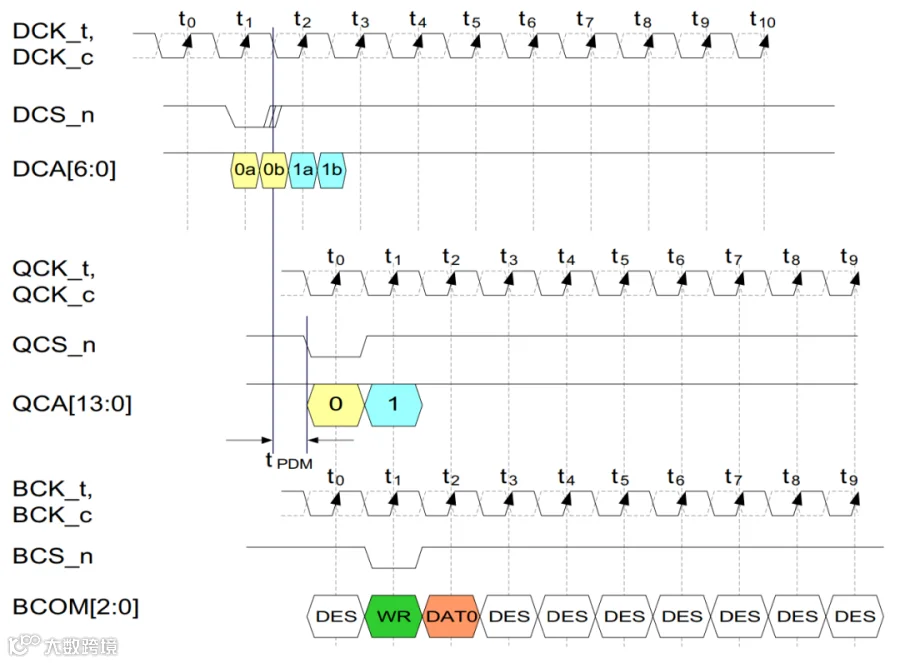

对DB的控制信号(RCD01/02/03支持,RCD04/05不支持DB接口)包括(每个通道)1 bit BCS,3 bit BCOM,1 bit BRST_n,1对差分BCK。BCOM信号在QCA后的一个周期进行驱动。如下图所示:

DDR5没有一个单独的CKE信号发送到DIMM或DRAM。Power Down模式(包括自我刷新),是通过一个UI命令发出信号的。根据电源进入命令,CS信号有效地成为CKE信号。静止的CS会使DRAM设备始终处于Power Down模式。CS的激活将使DRAM退出Power Down模式。当Host向CA总线上发送一个NOP命令,同时CS被激活,通过前述手段保证DRAM设备不再执行任何命令,从而进入Power Down模式。有或没有非目标ODT控制都不影响DRAM进入Power Down模式。

当所有DRAM级别都进入PDE电源关闭时,RCD进入低功耗模式;每个通道都可以独立进入PD模式。当子通道上的所有DRAM都进入断电状态时,RCD设备进入PD模式。当所有DRAM Rank都进入PD模式以后,RCD进入PD模式。主机发送PDE信号来让设备进入PD模式。输入端接电阻都被打开,输出可能被打开。QCA输出保持为高。PDE命令后的一个周期不能发送命令。PD模式的退出方式是,拉低DCS,并且发送一个NOP(PDX)命令。该命令不会检查校验。只有当最后一个Rank进入PD模式,PDE才会被发送给DB。当第一个PDX命令发出,DB就被唤醒(RCD04不支持DB接口)。

②PDE with ODT Control模式(RCD05不支持)

在这个模式下,下电的Rank和DB(RCD04不支持DB接口)依旧可以收到非目标ODT命令。RCD本身不进入掉电模式。QCA11决定进入带不带ODT控制的模式(1代表没有ODT控制,0代表有ODT控制)。该模式下,RCD可以传递带非目标ODT的WR/RD/MRR命令(CS在命令的两个UI都有效)。其他命令都不传递。当任意一个Rank接收非目标ODT命令,该命令应该被传到DB。有校验错误的情况下退出流程需要先发送PDX命令,再发送MRW命令清除校验错误状态,再次发送PDX命令。

③Self Refresh Mode with Clock Stop

SR w/ Clock Stop模式是一个非常低功耗的模式,输入时钟会停止。RCD和DRAM的输入端接电阻都被关闭。当所有通道的Rank都收到没有校验错误的SRE命令,主机将所有DCS信号拉低至少tCSSR。该操作下DCA信号不使用,也不做校验检查。RCD根据DCS信号拉低的时间来关闭输入端接电阻。主机会停止发送时钟,时钟可以是低电平或者浮空。PLL被关闭,DCS保持低以维持该状态。所有输出会被关闭,除了复位,以及QCS保持为低来让DRAM保持在SR模式。BCK、BCS和BCOM会被驱动为高或者high-Z。注意BCS不会被驱动低。当有DCS拉高,退出SR模式。RCD会重新使能输入ODT。当tSTAB01之后,允许通过Sideband配置频率,也可以重新Training。如果有DB,对应信号也需要重新Training。之后Host会发送NOP信号来让QCS拉高,以让DRAM的ODT生效。之后会连发三个NOP让DRAM退出SR模式。

④Self Refresh Mode without Clock Stop

没有时钟停止的自我刷新类似于有时钟停止模式的自我刷新,只是主机控制器将不会停止DCK输入。在两个子通道都接收到后,SRE命令主机通过向DCS[1:0]_[B:A]_n发送一个时钟宽的脉冲,而不是保持多次循环,使RCD进入这个模式。RCD将不会禁用其任何终止项,也将不会在没有时钟停止的自刷新期间禁用PLL。RCD也不会停止QCK或BCK时钟输出。退出此模式类似于使用时钟停止的自我刷新,只是主机在退出时不会等待tSTAB,因为PLL已经被锁定。由于DCS[x]_n信号已经很高了,所以退出的第一个指示是释放QCS[x]_n信号的NOPs。

为了让主机训练DRAM和DB接口(如果有DB接口),RCD将支持两种Pass Through模式:CA Pass Through模式和BCOM Pass Through模式(RCD04/05不支持)。注意不支持同时启用CA Pass Through模式和BCOM Pass Through模式。

无论DCS如何变化,DCA信号都会被传递给QCA。这允许主机发送多个周期的QCA设置/保持和多个周期的QCS变化,同时也以一个时钟周期粒度控制这些信号的持续时间和时间关系。在将RCD置入Pass Through模式之前,主机接口DCA必须保持稳定。通过配置RW07[4]=1来开启该模式。在通开启模式之前,必须禁用奇偶校验检查。DCS0和DCS1分别传到QCS0和QCS1,DCA直接传到QCA。可以选择DDR与SDR模式。当选择SDR模式,DPAR信号用于指示命令为前半(DPAR为低)还是后半(DPAR为高)。当RW07[5]=1,RCD忽略所有MRW命令,后续配置只能通过Sideband进行。

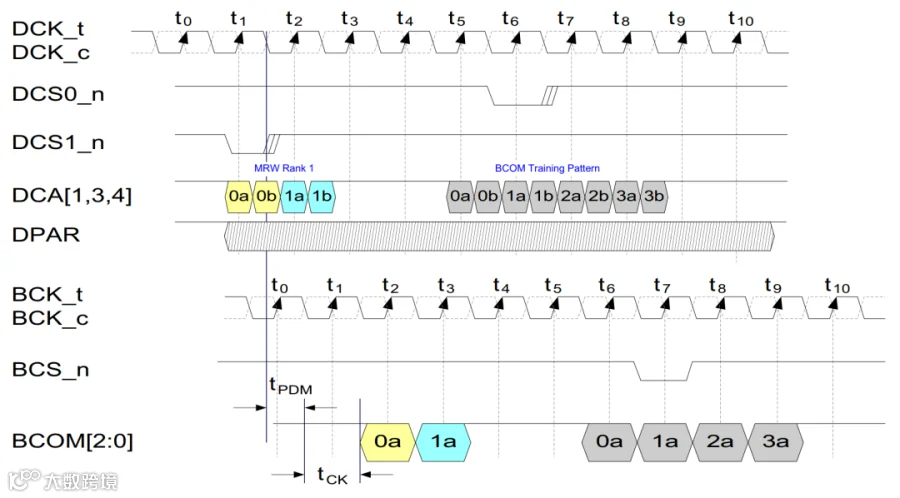

无论DCS如何变化,DCA4、DCA3、DCA1信号都会在BCOM总线上传递,DCS0_n被传递给BCS_n,但DCS1_n在此模式下不会被传递。相反,RCD将把针对RCD的MRW处理为如下图。这允许主机在BCOM训练期间控制BCOM和BCS模式的组合。在BCOM训练期间,主机必须设置DRAM接口阻塞。当启用了BCOM传递模式时,不需要DDR5 RCD01来将命令传输到QCA输出。当RW00[4] = 1时,将启用RCD BCOM Pass Through模式。在BCOM Pass Through模式下,不管是DDR还是SDR模式,RCD均对两个DCK上升边缘上的DCA4、DCA3和DCA1输入进行采样。如下图所示:

VHost模式允许在DRAM接口上发送一系列命令,而不通过主机接口接收命令。要在DRAM接口上发送的命令可以通过写入RCD控制字来编程。目的是在测试环境中通过宽带总线操作这个RCD特性。VHost模式主要用于测试,并不适用于正常操作。一系列的命令被编程到RCD中,然后通过写入一个起始MRW位来执行。

虚拟主机模式允许QCS和QCA不受DCS和DCA控制,而是直接发送一系列通过控制字寄存器设定的命令。最多可以一次性发送4个命令(单UI或双UI),其中CA[13:0]和片选都可以被定义。对于双UI命令,事实上可以编程为背靠背的两个单UI命令。每两个命令之间的时钟周期间隔可以单独定义,可以是2、4、8、16、64、256、1024个周期。最后一个命令之后,可以选择重复开始任一命令。带内MRW命令访问RW01寄存器会将虚拟主机模式锁定,直到下一次复位。

为了测试LRDIMM,RCD支持Transparent模式(透明模式)。当进入此模式时,RCD将自动禁用奇偶校验。要进入透明模式,主机首先发送一个带有RW82[0] = 1的MRW命令,以在DDR5DB01中启用透明模式。然后,它发送一个带有RW00[7] = 1的MRW命令,以在RCD中启用透明模式。在透明模式下,DDR5 DB01不解释BCS_n和BCOM命令。对于BCS_n输入值“1”和BCOM[2:0]输入值“111”,它将数据流从主机接口引导到DRAM接口。对于BCS_n输入值“1”和BCOM[2:0]输入值“000”,它将数据流从DRAM接口引导到主机接口。BCS_n和BCOM[2:0]的任何其他输入值都无效。此模式下,所有测试和正常运行的时钟频率都被支持。要退出透明模式,写RW00[7]=0,然后通过RW04的命令复位DB,让DB退出透明模式。

DDR5没有一个单独的CKE信号发送到DIMM或DRAM。Power Down模式(包括自我刷新),是通过一个UI命令发出信号的。根据电源进入命令,CS信号有效地成为CKE信号。静止的CS会使DRAM设备始终处于Power Down模式。CS的激活将使DRAM退出Power Down模式。当Host向CA总线上发送一个NOP命令,同时CS被激活,通过前述手段保证DRAM设备不再执行任何命令,从而进入Power Down模式。有或没有非目标ODT控制都不影响DRAM进入Power Down模式。

当所有DRAM级别都进入PDE电源关闭时,RCD进入低功耗模式;每个通道都可以独立进入PD模式。当子通道上的所有DRAM都进入断电状态时,RCD设备进入PD模式。当所有DRAM Rank都进入PD模式以后,RCD进入PD模式。主机发送PDE信号来让设备进入PD模式。输入端接电阻都被打开,输出可能被打开。QCA输出保持为高。PDE命令后的一个周期不能发送命令。PD模式的退出方式是,拉低DCS,并且发送一个NOP(PDX)命令。该命令不会检查校验。只有当最后一个Rank进入PD模式,PDE才会被发送给DB。当第一个PDX命令发出,DB就被唤醒(RCD04不支持DB接口)。

②PDE with ODT Control模式(RCD05不支持)

在这个模式下,下电的Rank和DB(RCD04不支持DB接口)依旧可以收到非目标ODT命令。RCD本身不进入掉电模式。QCA11决定进入带不带ODT控制的模式(1代表没有ODT控制,0代表有ODT控制)。该模式下,RCD可以传递带非目标ODT的WR/RD/MRR命令(CS在命令的两个UI都有效)。其他命令都不传递。当任意一个Rank接收非目标ODT命令,该命令应该被传到DB。有校验错误的情况下退出流程需要先发送PDX命令,再发送MRW命令清除校验错误状态,再次发送PDX命令。

③Self Refresh Mode with Clock Stop

SR w/ Clock Stop模式是一个非常低功耗的模式,输入时钟会停止。RCD和DRAM的输入端接电阻都被关闭。当所有通道的Rank都收到没有校验错误的SRE命令,主机将所有DCS信号拉低至少tCSSR。该操作下DCA信号不使用,也不做校验检查。RCD根据DCS信号拉低的时间来关闭输入端接电阻。主机会停止发送时钟,时钟可以是低电平或者浮空。PLL被关闭,DCS保持低以维持该状态。所有输出会被关闭,除了复位,以及QCS保持为低来让DRAM保持在SR模式。BCK、BCS和BCOM会被驱动为高或者high-Z。注意BCS不会被驱动低。当有DCS拉高,退出SR模式。RCD会重新使能输入ODT。当tSTAB01之后,允许通过Sideband配置频率,也可以重新Training。如果有DB,对应信号也需要重新Training。之后Host会发送NOP信号来让QCS拉高,以让DRAM的ODT生效。之后会连发三个NOP让DRAM退出SR模式。

④Self Refresh Mode without Clock Stop

没有时钟停止的自我刷新类似于有时钟停止模式的自我刷新,只是主机控制器将不会停止DCK输入。在两个子通道都接收到后,SRE命令主机通过向DCS[1:0]_[B:A]_n发送一个时钟宽的脉冲,而不是保持多次循环,使RCD进入这个模式。RCD将不会禁用其任何终止项,也将不会在没有时钟停止的自刷新期间禁用PLL。RCD也不会停止QCK或BCK时钟输出。退出此模式类似于使用时钟停止的自我刷新,只是主机在退出时不会等待tSTAB,因为PLL已经被锁定。由于DCS[x]_n信号已经很高了,所以退出的第一个指示是释放QCS[x]_n信号的NOPs。

为了让主机训练DRAM和DB接口(如果有DB接口),RCD将支持两种Pass Through模式:CA Pass Through模式和BCOM Pass Through模式(RCD04/05不支持)。注意不支持同时启用CA Pass Through模式和BCOM Pass Through模式。

无论DCS如何变化,DCA信号都会被传递给QCA。这允许主机发送多个周期的QCA设置/保持和多个周期的QCS变化,同时也以一个时钟周期粒度控制这些信号的持续时间和时间关系。在将RCD置入Pass Through模式之前,主机接口DCA必须保持稳定。通过配置RW07[4]=1来开启该模式。在通开启模式之前,必须禁用奇偶校验检查。DCS0和DCS1分别传到QCS0和QCS1,DCA直接传到QCA。可以选择DDR与SDR模式。当选择SDR模式,DPAR信号用于指示命令为前半(DPAR为低)还是后半(DPAR为高)。当RW07[5]=1,RCD忽略所有MRW命令,后续配置只能通过Sideband进行。

无论DCS如何变化,DCA4、DCA3、DCA1信号都会在BCOM总线上传递,DCS0_n被传递给BCS_n,但DCS1_n在此模式下不会被传递。相反,RCD将把针对RCD的MRW处理为如下图。这允许主机在BCOM训练期间控制BCOM和BCS模式的组合。在BCOM训练期间,主机必须设置DRAM接口阻塞。当启用了BCOM传递模式时,不需要DDR5 RCD01来将命令传输到QCA输出。当RW00[4] = 1时,将启用RCD BCOM Pass Through模式。在BCOM Pass Through模式下,不管是DDR还是SDR模式,RCD均对两个DCK上升边缘上的DCA4、DCA3和DCA1输入进行采样。如下图所示:

VHost模式允许在DRAM接口上发送一系列命令,而不通过主机接口接收命令。要在DRAM接口上发送的命令可以通过写入RCD控制字来编程。目的是在测试环境中通过宽带总线操作这个RCD特性。VHost模式主要用于测试,并不适用于正常操作。一系列的命令被编程到RCD中,然后通过写入一个起始MRW位来执行。

虚拟主机模式允许QCS和QCA不受DCS和DCA控制,而是直接发送一系列通过控制字寄存器设定的命令。最多可以一次性发送4个命令(单UI或双UI),其中CA[13:0]和片选都可以被定义。对于双UI命令,事实上可以编程为背靠背的两个单UI命令。每两个命令之间的时钟周期间隔可以单独定义,可以是2、4、8、16、64、256、1024个周期。最后一个命令之后,可以选择重复开始任一命令。带内MRW命令访问RW01寄存器会将虚拟主机模式锁定,直到下一次复位。

为了测试LRDIMM,RCD支持Transparent模式(透明模式)。当进入此模式时,RCD将自动禁用奇偶校验。要进入透明模式,主机首先发送一个带有RW82[0] = 1的MRW命令,以在DDR5DB01中启用透明模式。然后,它发送一个带有RW00[7] = 1的MRW命令,以在RCD中启用透明模式。在透明模式下,DDR5 DB01不解释BCS_n和BCOM命令。对于BCS_n输入值“1”和BCOM[2:0]输入值“111”,它将数据流从主机接口引导到DRAM接口。对于BCS_n输入值“1”和BCOM[2:0]输入值“000”,它将数据流从DRAM接口引导到主机接口。BCS_n和BCOM[2:0]的任何其他输入值都无效。此模式下,所有测试和正常运行的时钟频率都被支持。要退出透明模式,写RW00[7]=0,然后通过RW04的命令复位DB,让DB退出透明模式。

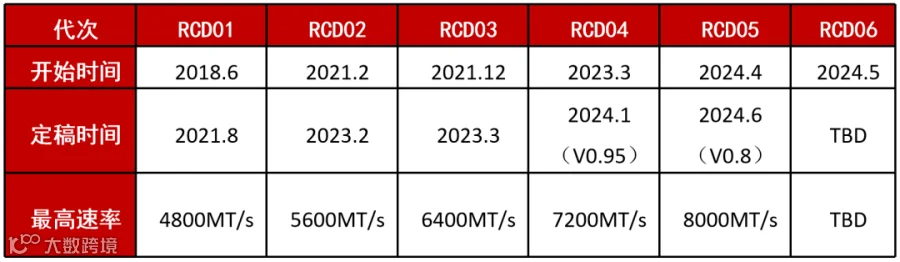

RCD01/02/03主要是速率上的变化、QCA delay control的设计发展以及training上的一些优化调整;

RCD04除了速率提高外,最大的变化就是不再支持DB接口;

RCD05与前几代RCD相比变化很大,封装的Ball数量都变化了(从240 Ball修改为264 Ball),主要是因为给DRAM的Clock Outputs(QCK)从4 Copy变成了8 Copy。

关于RCD的发展还在继续讨论中,RCD作为DDR5 DIMM的重要组成部分,其发展过程也从另一个维度体现了DDR5 DIMM的发展。

RCD(寄存器时钟驱动器)作为内存模块的重要组成部分,具备高效、低功耗、稳定可靠等特性,广泛应用于各种内存,如DDR4/DDR5 RDIMM,DDR4/DDR5 LRDIMM等。随着DDR5及未来DDR6等新一代内存技术的不断发展,RCD将继续发挥重要作用,RCD的设计和制造也将不断创新,以满足这些未来需求。

牛芯半导体(深圳)有限公司(简称“牛芯半导体”)成立于2020年,聚焦接口IP的开发和授权,并提供相关整体解决方案,致力成为全球领先的IP供应商。

基于自主可控的核心技术,牛芯半导体在主流先进工艺布局SerDes、DDR等中高端接口IP,产品广泛应用于消费电子、网络通信、数据存储、人工智能、汽车电子、医疗电子等领域。

未来,牛芯半导体持续响应IP国产化需求,适应不断演进的接口技术和日益拓展的接口互联场景,赋能数智时代下的千行百业。