本文转载自TrustZone,转载文章仅供学习和研究使用。

在大数据早已普及的今日,尤其随着5G技术和移动设备的逐渐普及,各种有线或无线的传输技术也迎来了迅猛发展,内容日新月异、错综复杂,你又能窥探其中多少呢?本文将主要基于CSI-2,简单介绍高速影音传输技术MIPI。

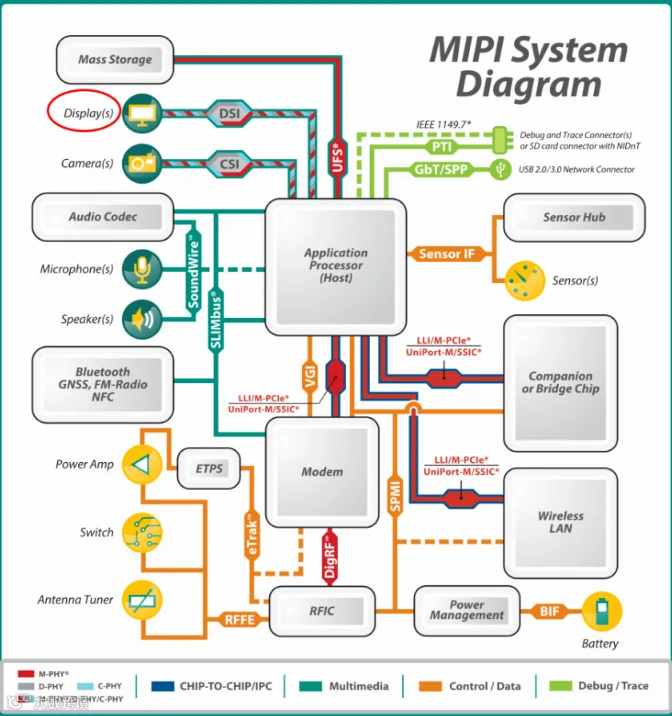

MIPI(Mobile Industry Processor Interface,移动产业处理器接口) Alliance,即MIPI联盟发起并为移动应用处理器制定了开放标准和一种规范。主要是手机内部的接口(摄像头、显示屏接口、射频/基带接口)等标准化,从而减少手机内部接口的复杂程度及增加设计的灵活性。

MIPI联盟下面有不同的工作组,分别定义的一系列接口标准,比如CSI(Camera Serial Interface,摄像头串行接口)、DSI(Display Serial Interface,显示串行接口)、DigRF(射频接口)、SLIMBUS(麦克风、喇叭接口)等,其优点是更低功耗,更高数据传输数量和更小的空间。

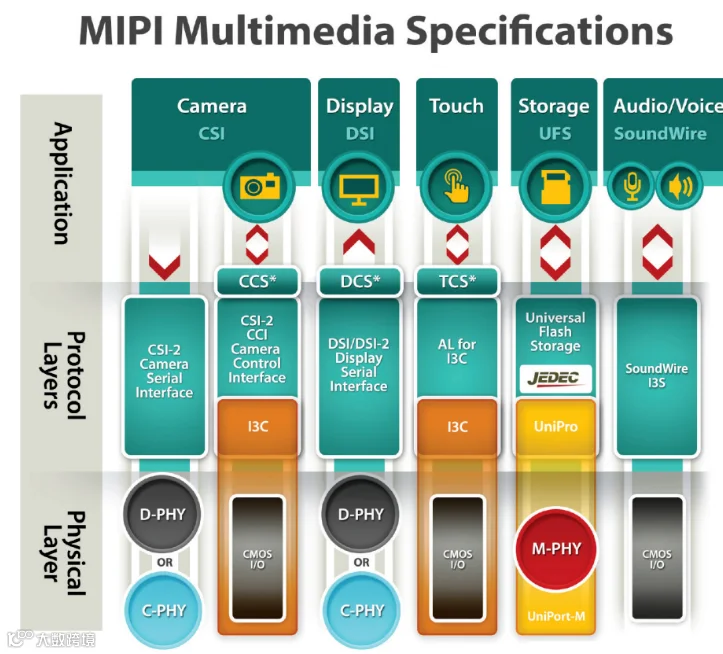

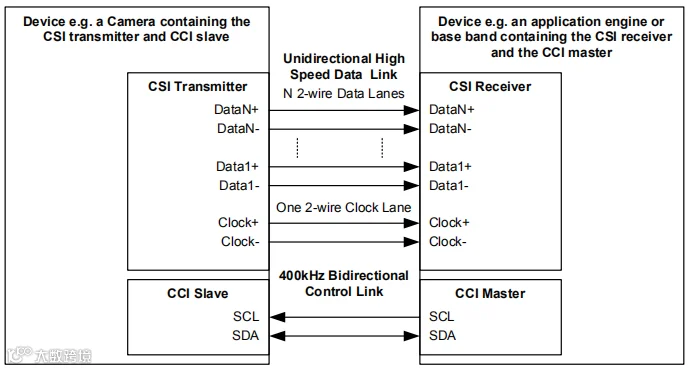

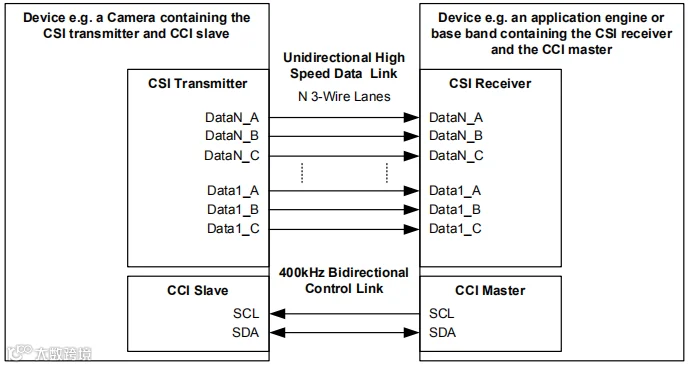

CSI-2替MIPI定义了两种高速数据传输接口(物理层选项)和一组控制接口的标准。

-

-

-

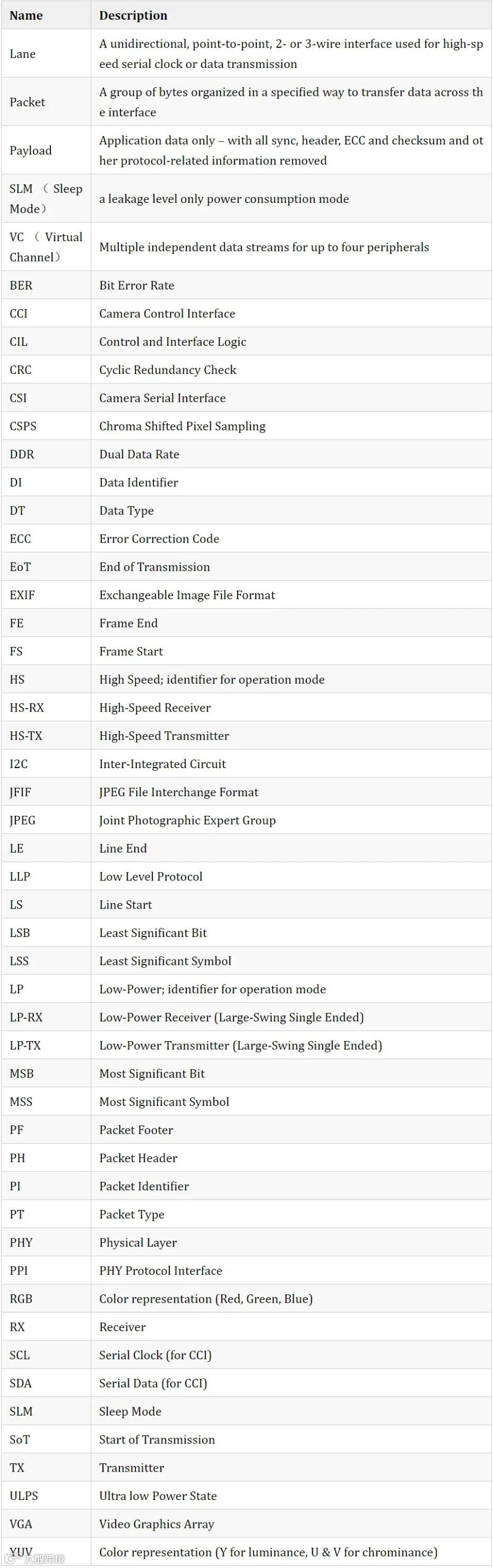

CCI(Camera Control Interface)

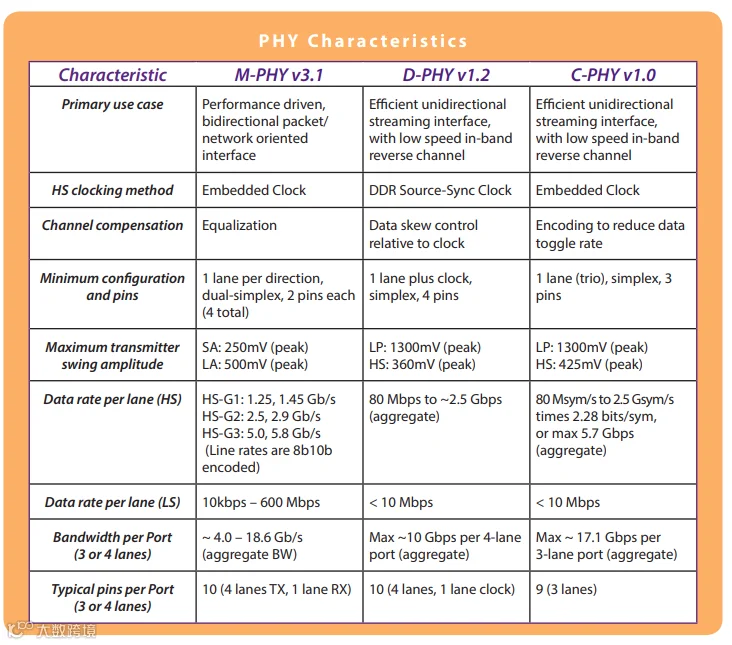

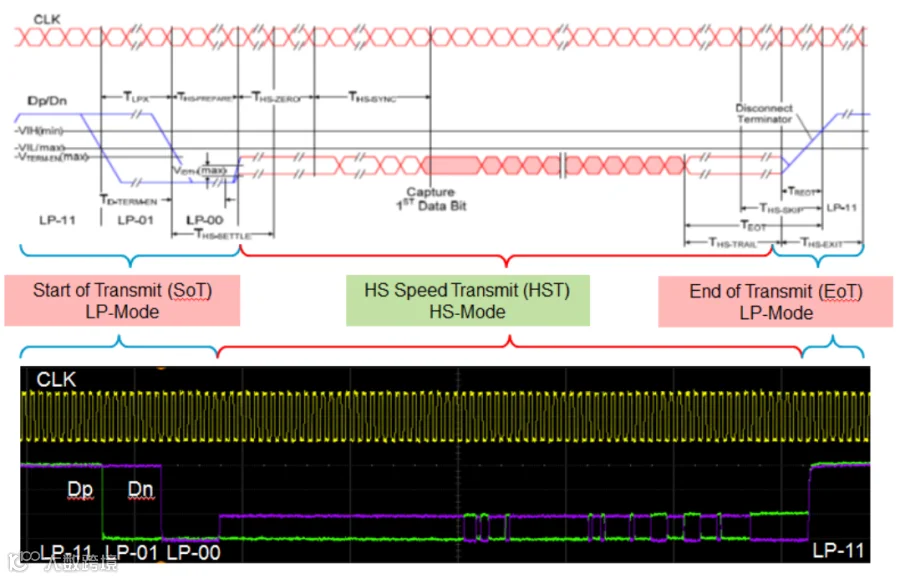

MIPI联盟定义的常见的D-PHY接口支持高速(HS)和低速(LP)模式,为1路单向差分接口,分为:

-

-

-

CCI(Camera Control Interface)

另一种常见的C-PHY接口,为1或多路单向3-wire串行数据通道,每路有自己的时钟。

聊到了C-PHY和D-PHY,也顺便提一下M-PHY,M-PHY目前接触比较少, 其在功耗和性能方面有更多的考量,三种PHY的特性如下:

参见如上两幅图片的CCI部分。D-PHY和C-PHY的CCI接口是一组与I2C标准协议兼容的双向控制接口,兼容I2C的高速模式(400 KHZ)和7位从设备地址,不支持多主设备模式。CCI是I2C协议的一个子集,然后其在I2C上面定义了一个附加的数据协议层。详见CSI-2 Spec。

-

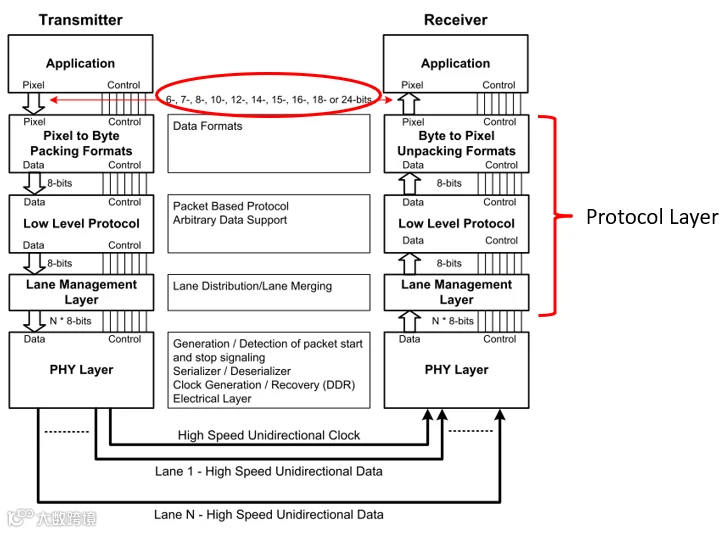

物理层(PHY Layer):定义传输媒介、电器特性、IO电路、同步机制指定SoT(Start of Transmission)和EoT(End of Transmission)信号等。如M-PHY、D-PHY、C-PHY等。

-

协议层(Protocol Layer):定义传输数据时,如何标记和交错多个数据流(Data Stream),以便接收端重建每个数据流。

-

应用层(Application Layer):对数据流进行处理,如分析、编解码。

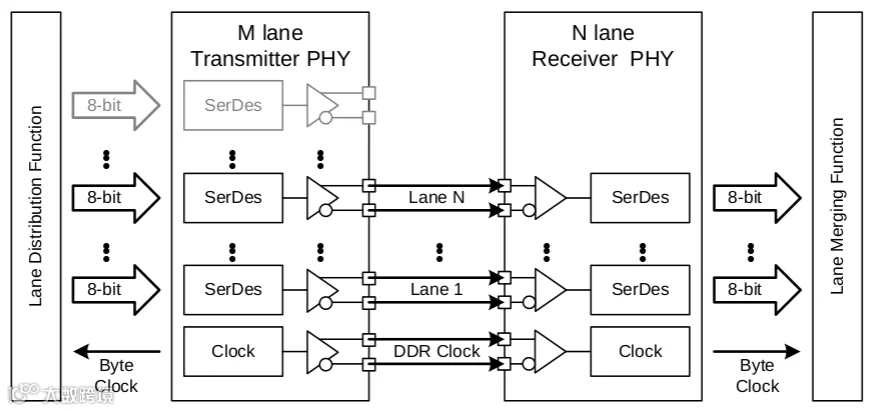

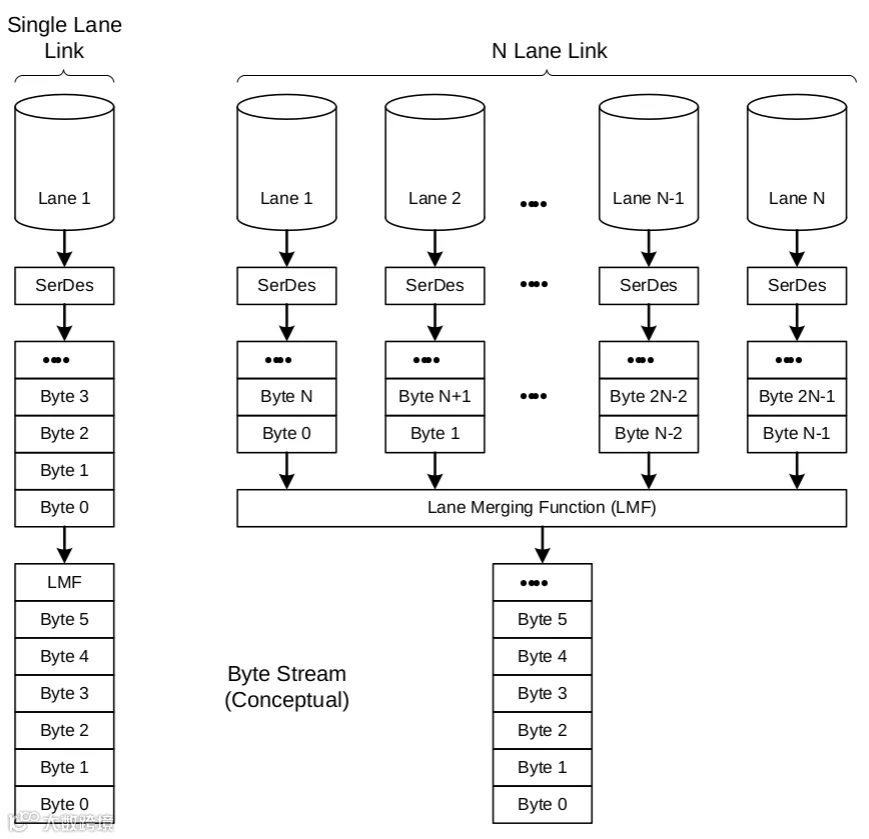

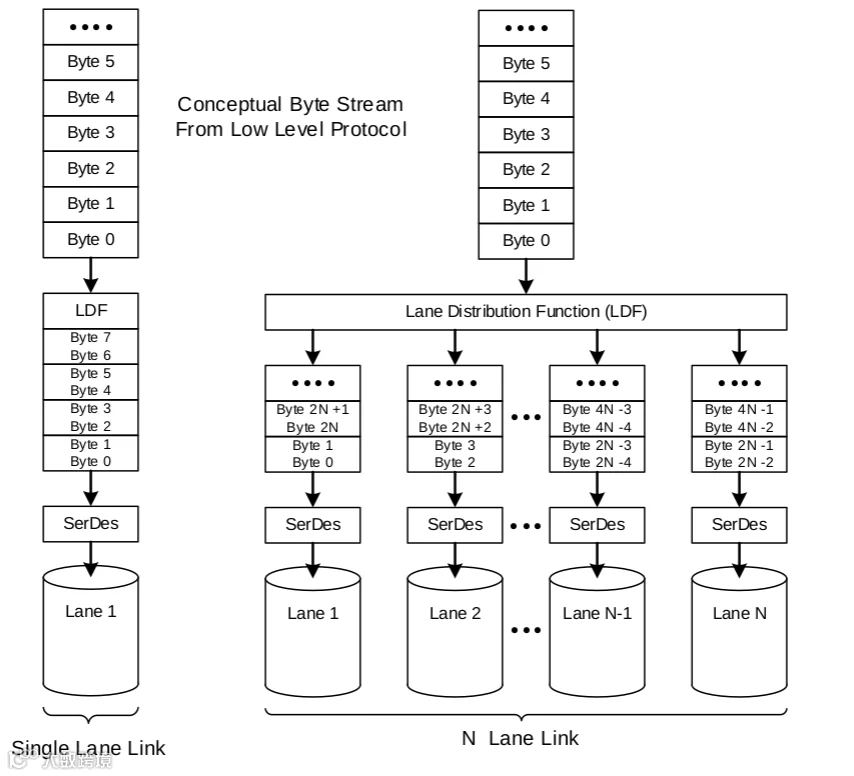

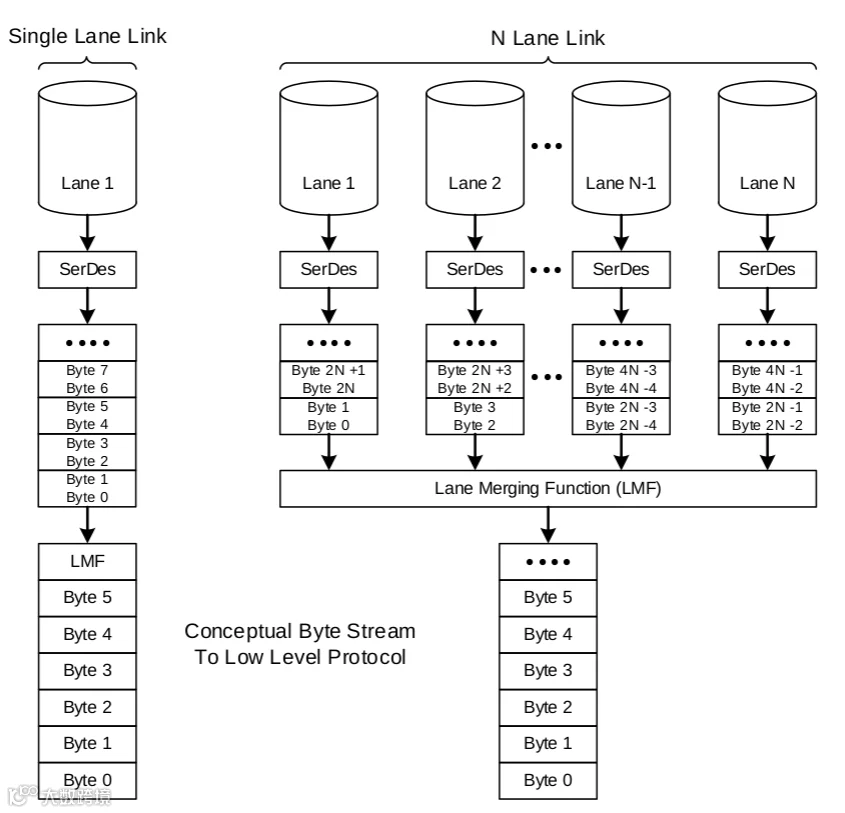

Multi-Lane Distribution and Merging

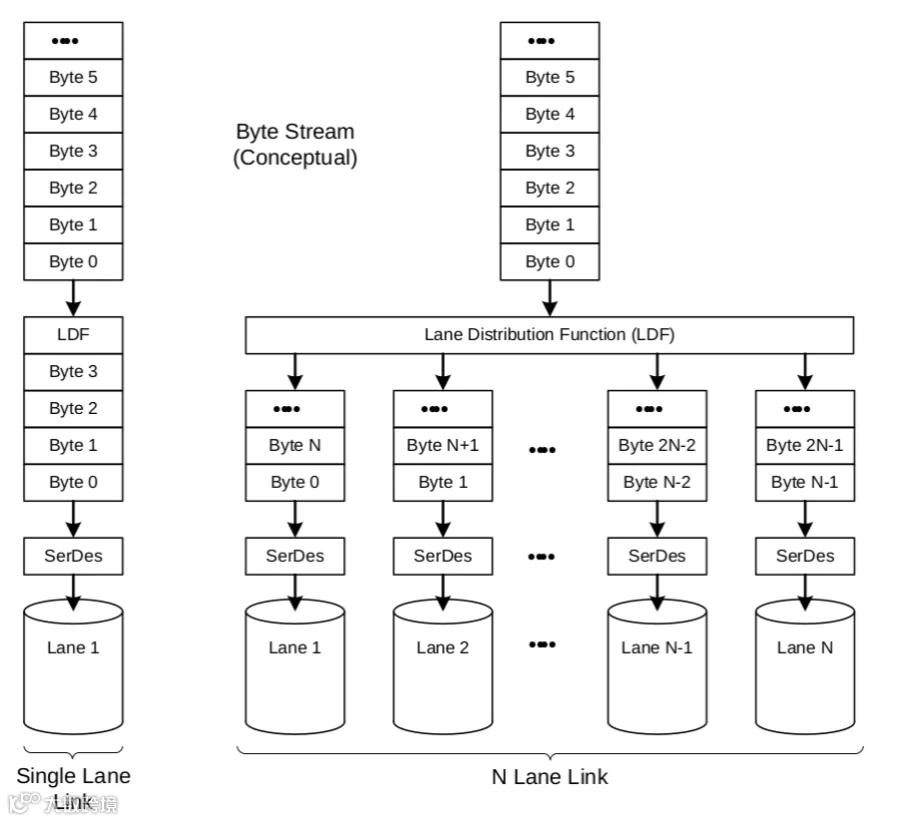

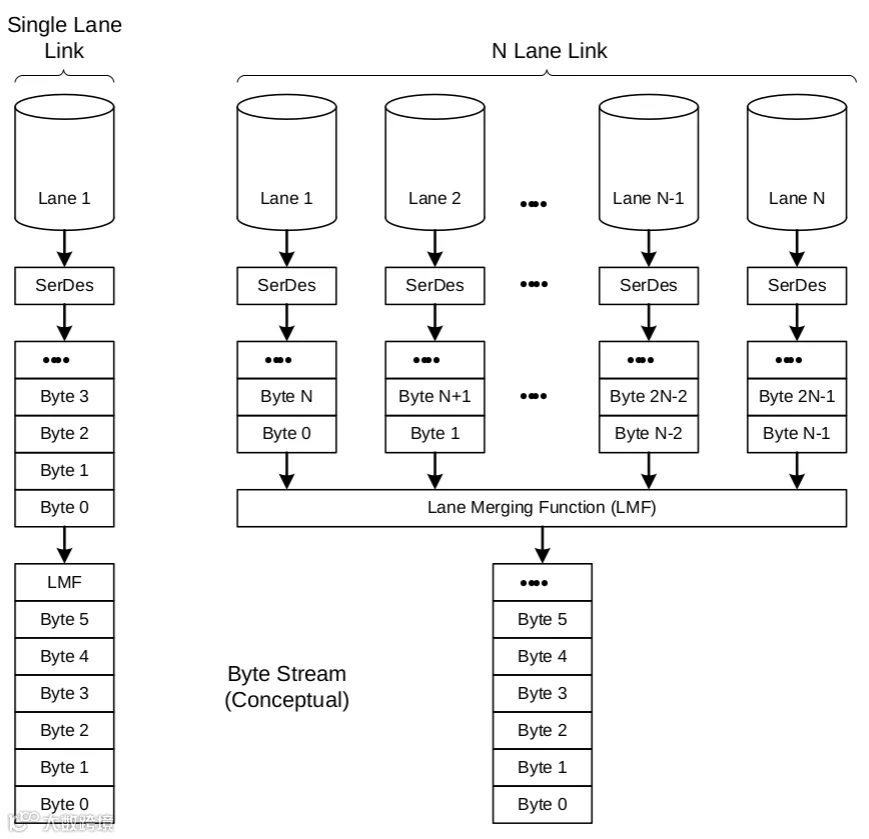

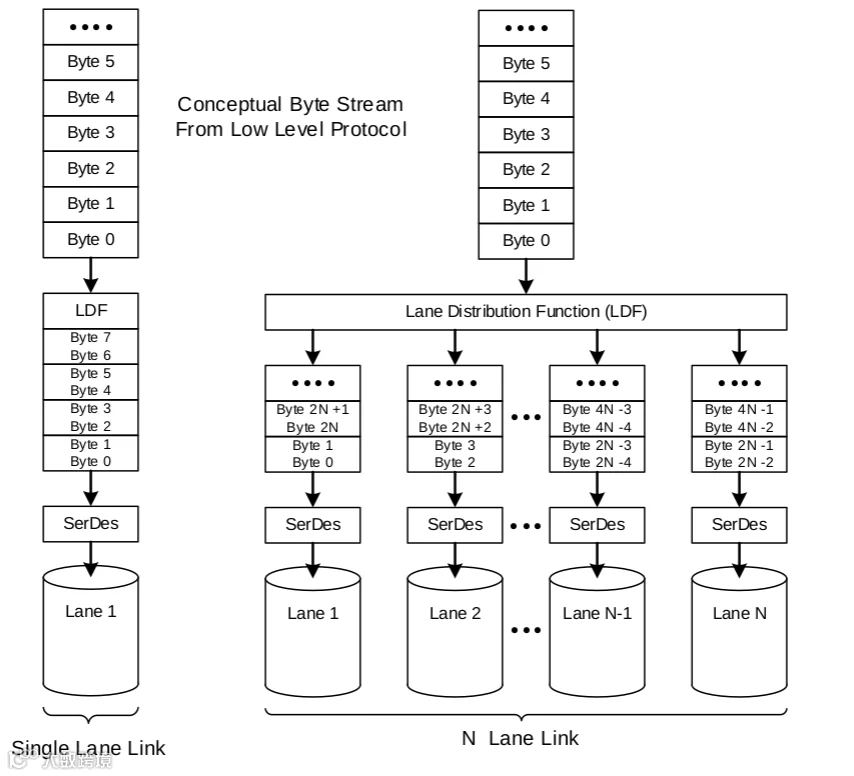

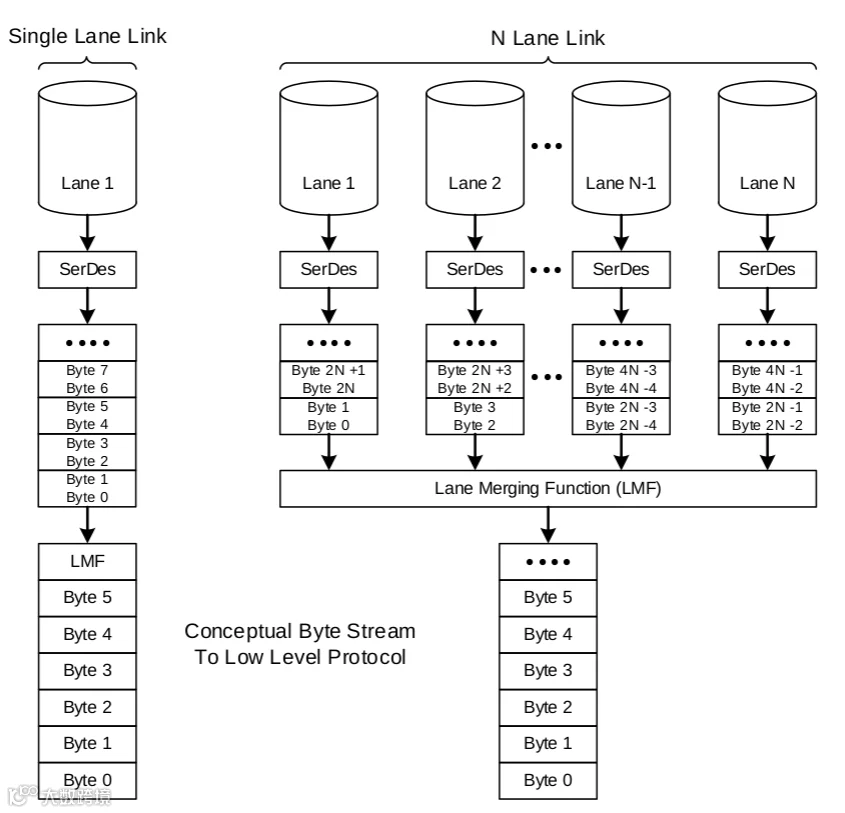

MIPI会通过CSI的LDF(Lane Distribution Function))将数据平均且有序地分配到每一条Lane。

Multi-Lane Interoperability

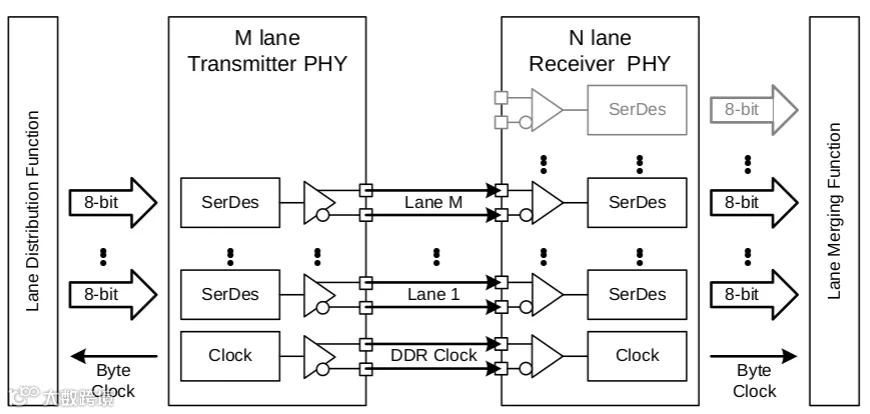

一般会采用最通用硬件配置,譬如D-PHY的4组Data Lan和1组Clock。但是有时也会存在发送端和接收端Data Lan不匹配的问题,如果使用不适当的配置,就会影响MIPI传输的性能。

譬如:M Lanes的传输端,N Lanes的接收端。

1. M <= N,传输端小于等于接收端时,不会有性能问题。

2. M > N,传输断大于接收端时,就会有性能问题。

-

通道管理(Lane Management):将传输的数据流分配到一个或多个通道,并在接收端恢复原始数据流。

-

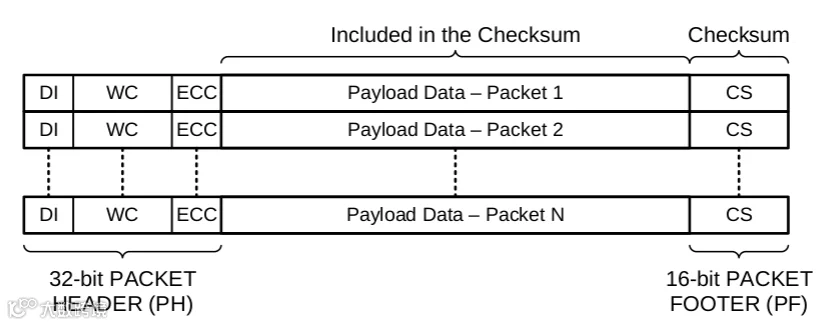

LLP(Low Level Protocol):将数据里封装成不同形式的长包和短包。

-

封拆像素包(Pixel Packing/Unpacking):传输端将像素包拆为bytes,接收端将bytes还原。

LLP(Low Level Protocol)是一种面向字节、基于数据包的协议,支持使用短包和长包格式传输任意数据。主要特性如下:

-

-

每link支持最多4个VC(Virtual Channels)通道

-

数据的类型、像素深度和格式的描述符(type,pixel depth and format)

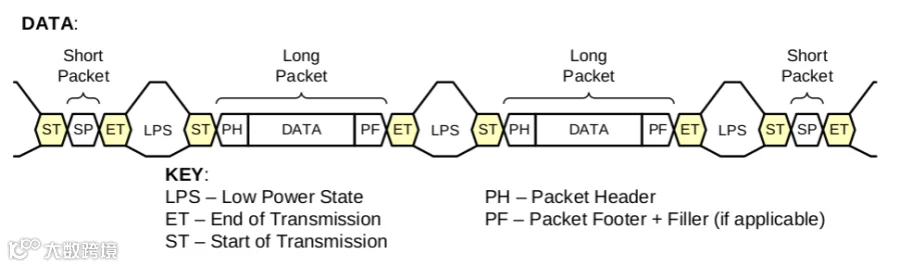

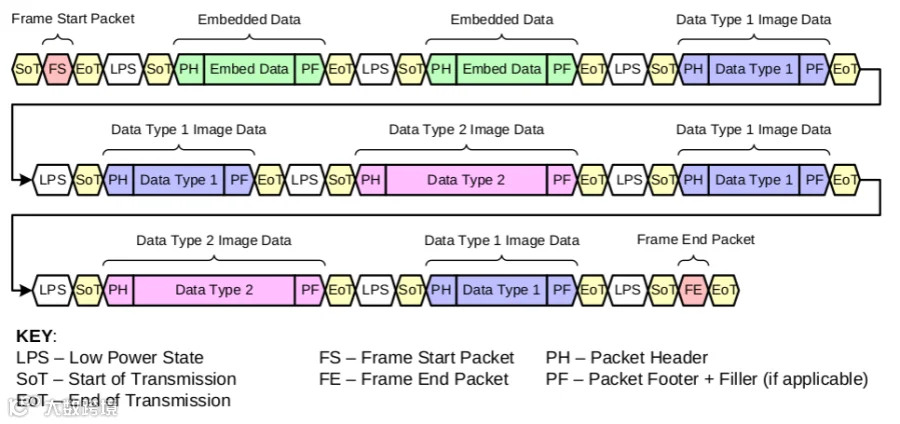

如下图所示,有长包和短包两种数据包结构,其格式和大小依赖于物理层的选择(D-PHY or C-PHY)。每种物理层接口都是以退出低功耗状态(LPS, Low Power State),发送一个SOT短包作为开始,然后通过长包发送数据,最后以发送一个EoT短包,切换回低功耗状态为结束。

长包由DT值0x10~0x37进行标识,详情见Data Type(DT)章节。

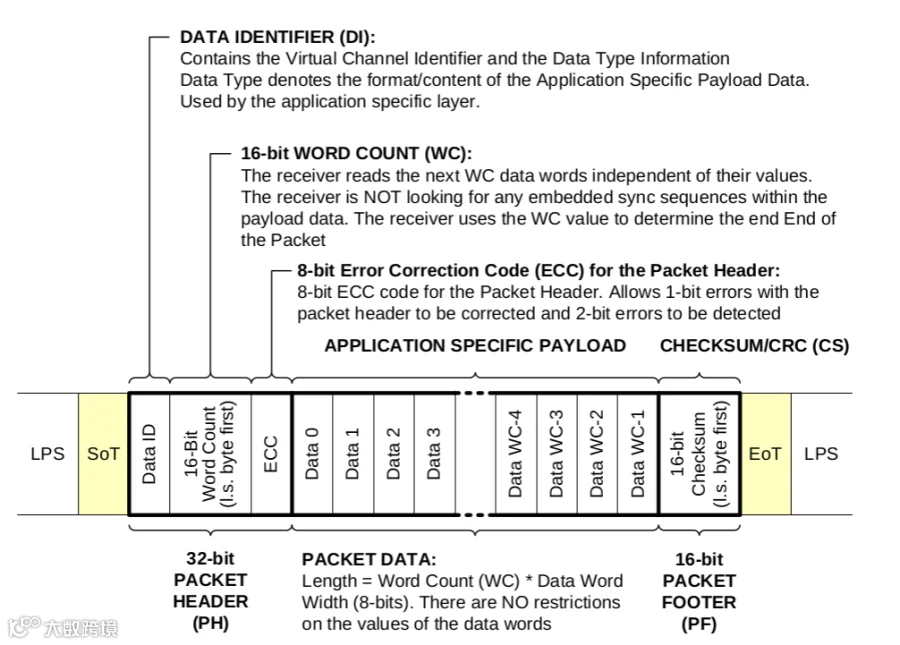

What does D-PHY Long Packet look like?

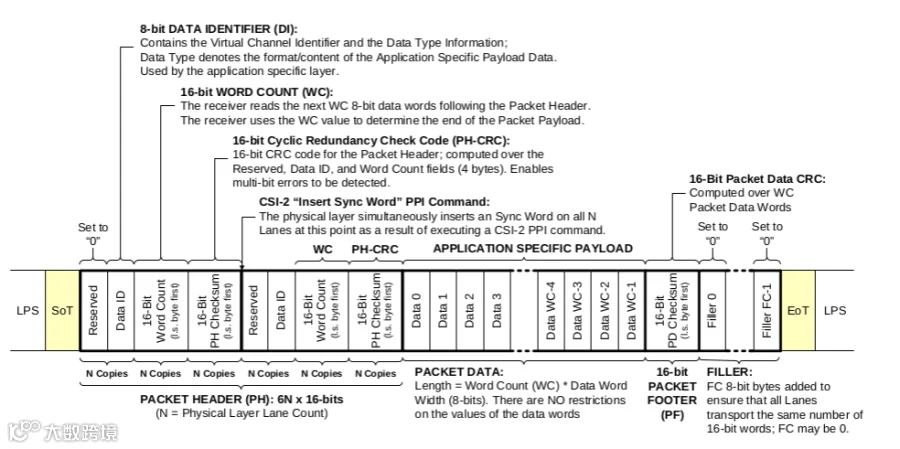

What does C-PHY Long Packet look like?

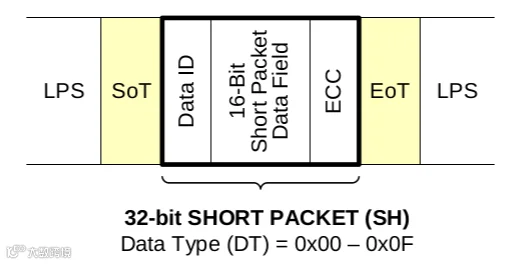

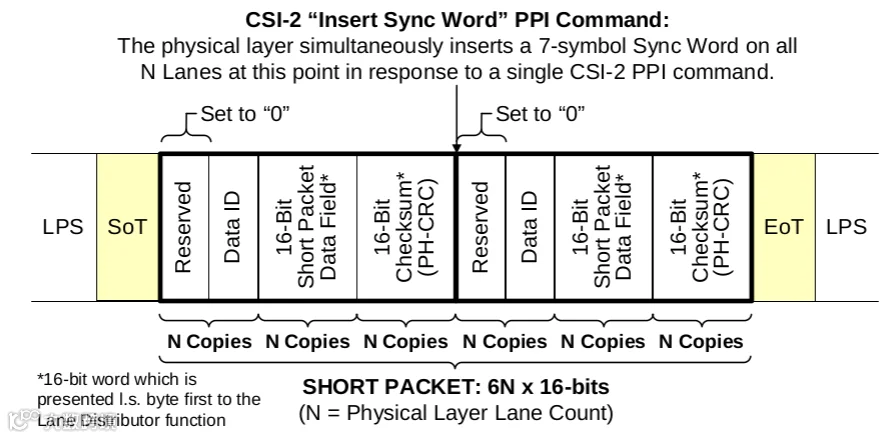

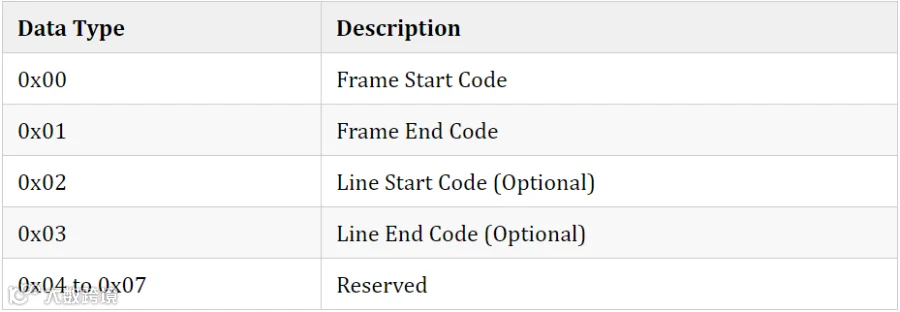

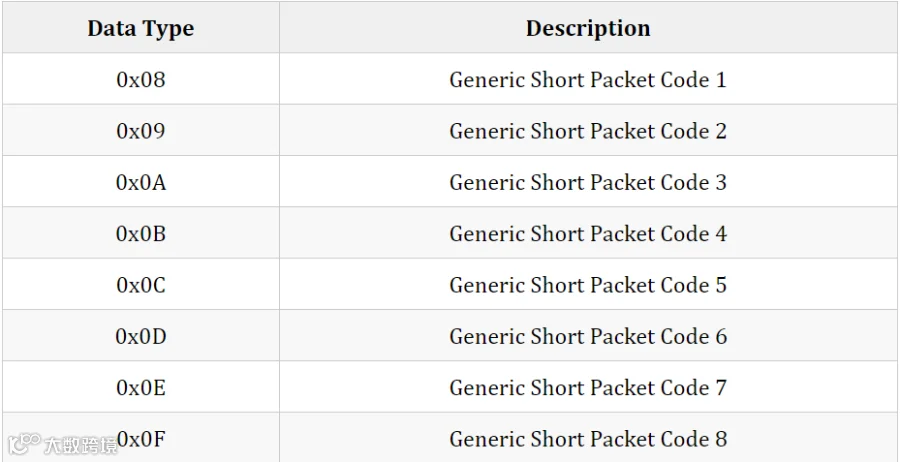

D-PHY和C-PHY的短包有一定的差异,短包与相应协议长包的包头(PH)相匹配,没有包脚(PF)和长包数据(Paket Filler),另需把包头的WC字段用短包数据替换,短包的数据由DT值0x00~0x0F标示。详情见Data Type(DT)章节。

对于帧同步短包,短包数据为帧号;对于行同步短包,短包数据为行号;对于通用短包,短包数据为用户自定义。

What does D-PHY Short Packet look like?

What does C-PHY Short Packet look like?

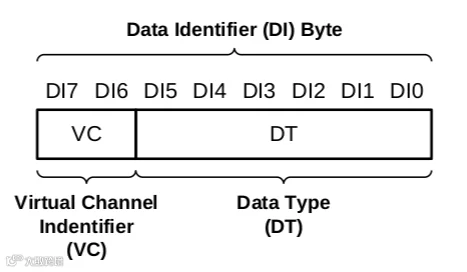

DI字节由VC(Virtual Chanel)和DT(Data Type)两部分组成。如下图:

Virtual Chanel Identifier

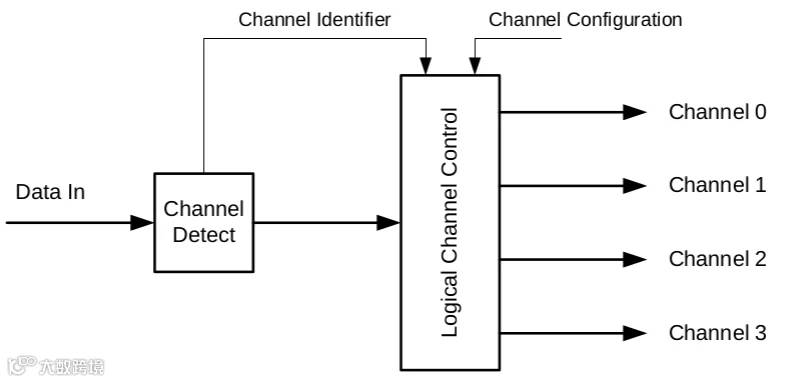

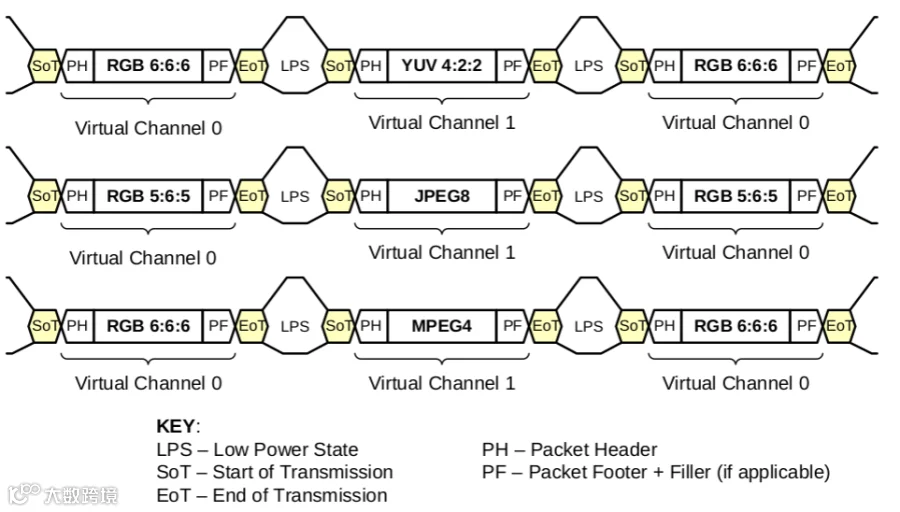

虚拟通道标识符是为数据流中交错的不同数据流提供单独的通道,接收器会监控并拆分交错的数据流到合适的通道。MIPI联盟规定最多可以支持4路数据流,也就是4路VC。外设中的虚拟通道标识符应该是可编程的,以允许主机处理器控制数据流的解复用方式。逻辑信道的原理如下图:

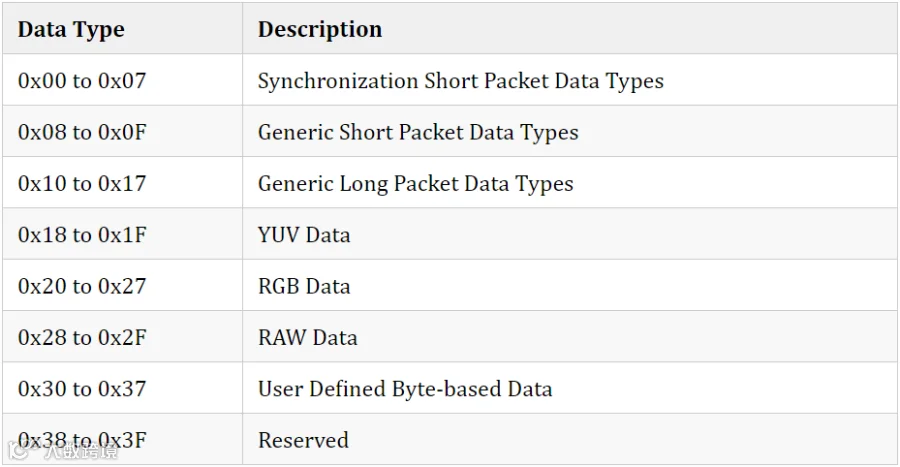

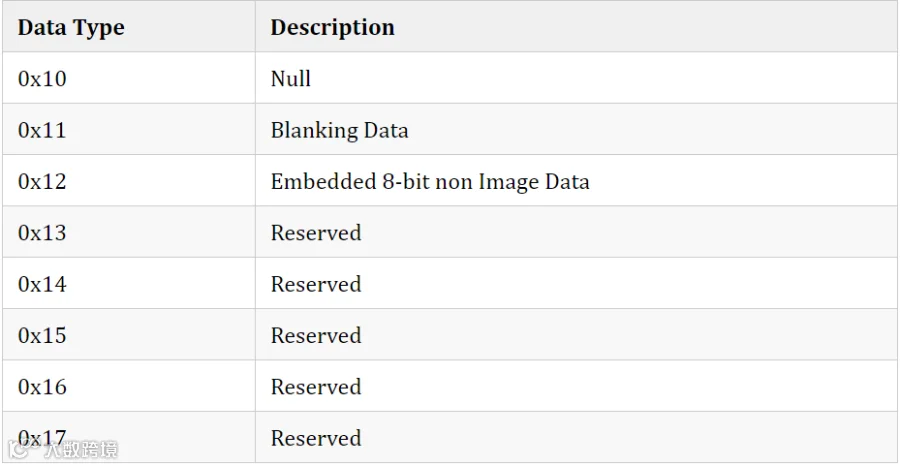

DT指定数据的格式和内容,支持最大64个DT,总共有8种不同的类型,每种支持8个DT,前两个类型代表短包,其余的代表长包。如下:

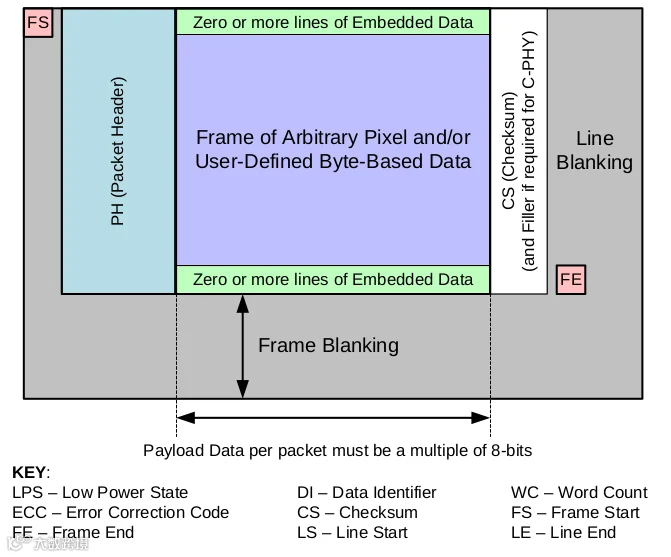

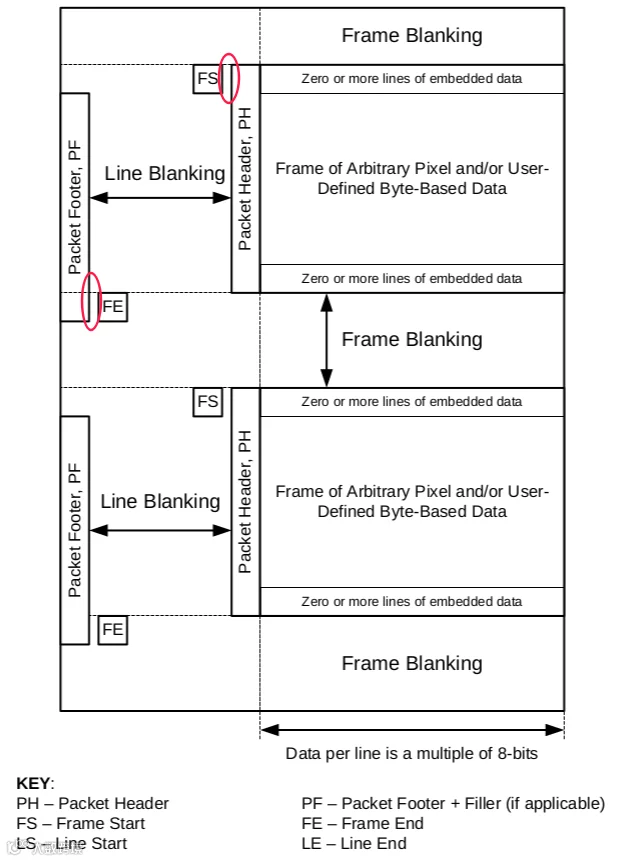

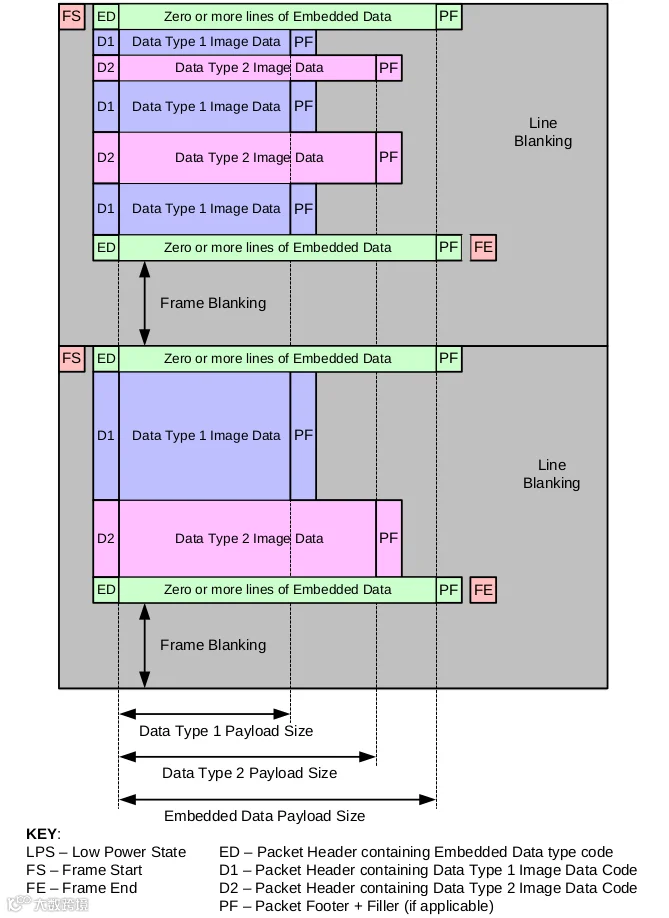

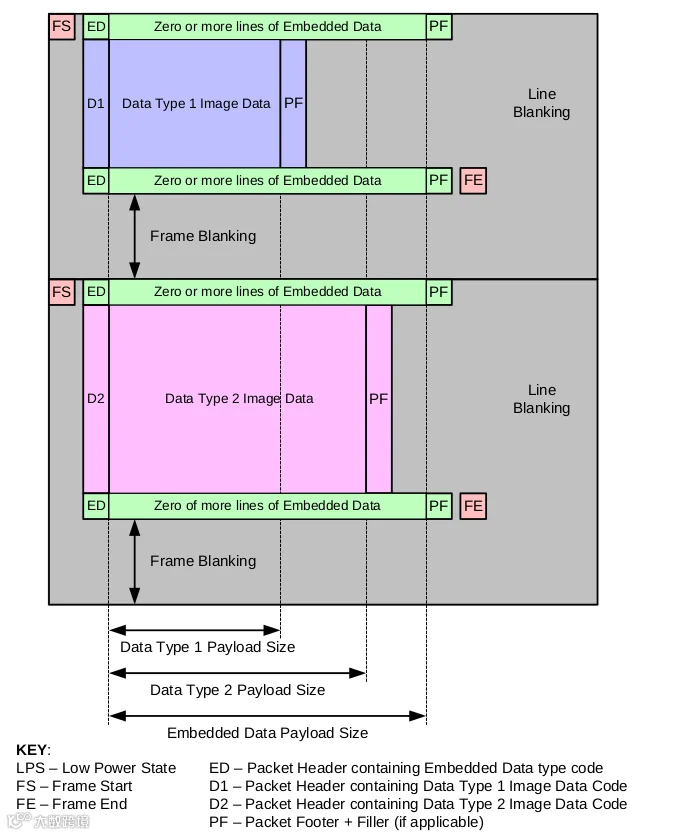

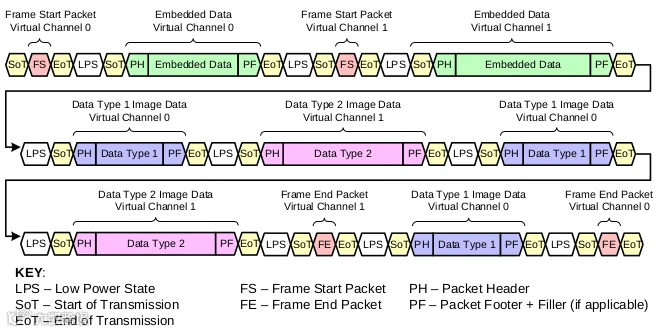

接收端需要忽略Null和Blanking Data数据类型的包的内容,空包(Null)没有任何意义,消隐包(Blanking Data)可以作为视频流帧之间的消隐行。在帧的开头可能有0或多行嵌入数据,这部分被称之为帧头(FS),在帧的末尾可能有0或多行嵌入数据,这部分被称之为帧尾。如果行存在Embedded数据,则DI中需要包含其DT。如下图:

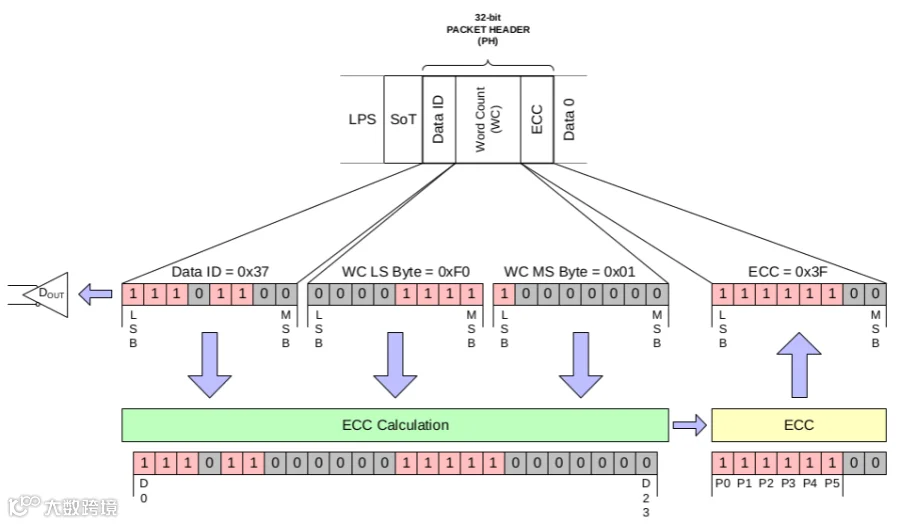

Error Correction Code (ECC)

for D-PHY

包头的ECC允许纠正DI和WC的1-bit错误并为D-PHY检测2-bit错误,因此, ECC的 D[7:6] 应该为0。DI[7:0] 应映射到ECC输入的 D[7:0],WC[7:0] 映射到 D[15:8], WC[15:8] 映射到 D[23:16]。如下图:

Checksum Generation for C-PHY

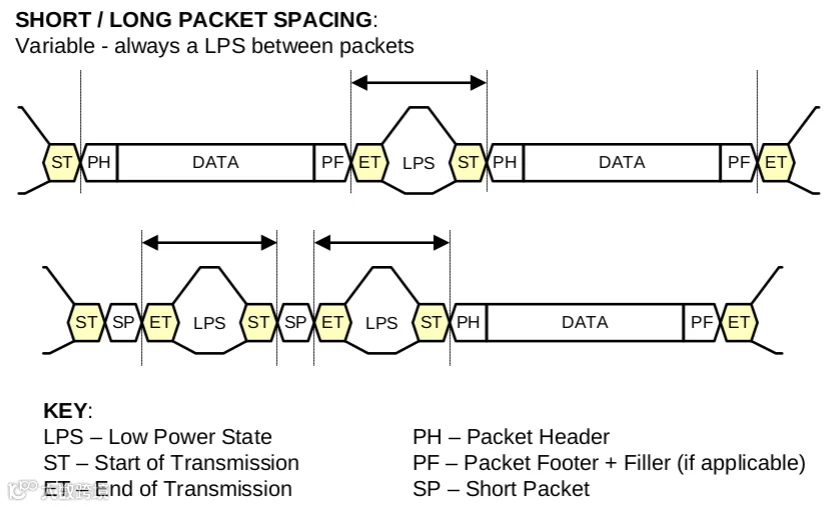

MIPI数据包由EoT,LPS,SoT分隔开,在协议包之间必须有一个进入和退出 LPS(低功耗)的状态切换,称之为包间隔(Packet Spacing)。其不必是8位字的倍数,因为接收器将在下一个数据包的包头之前的SoT序列期间重新同步到正确的字节边界。

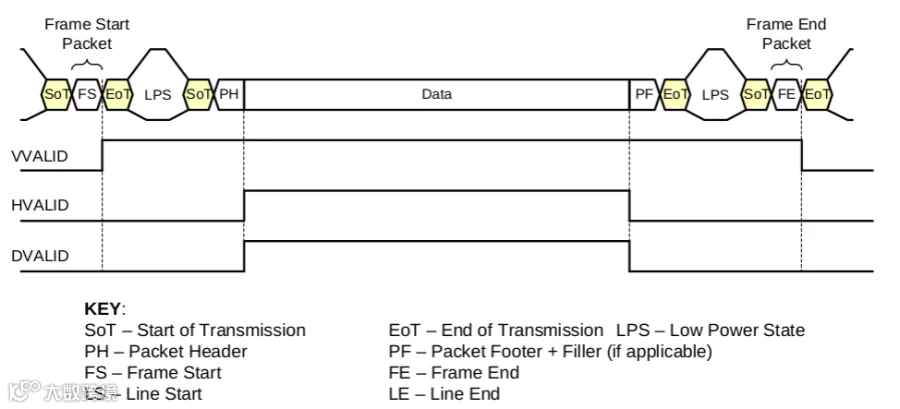

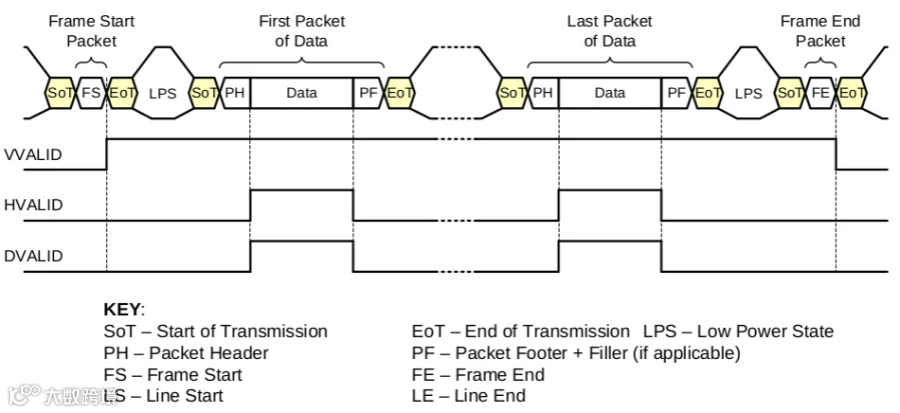

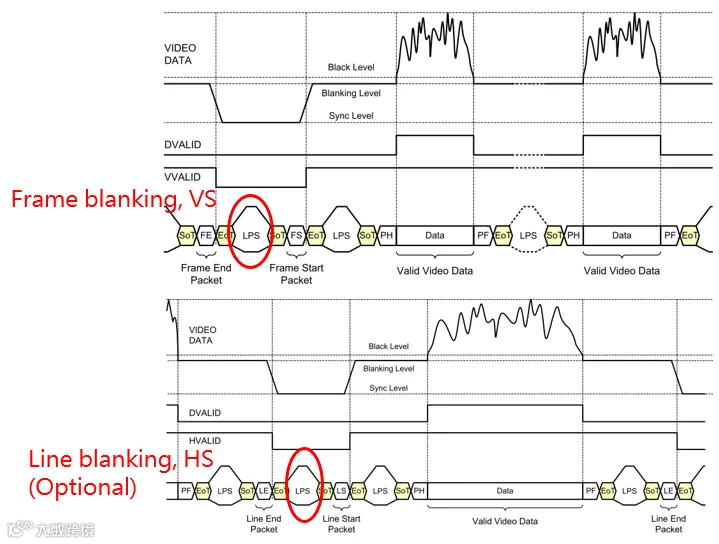

图中的VVALID、HVALID和DVALID为虚拟的帧同步(VSYNC)、行同步(HSYNC)和有效数据同步(DE,亦可称为数据使能信号)信号。

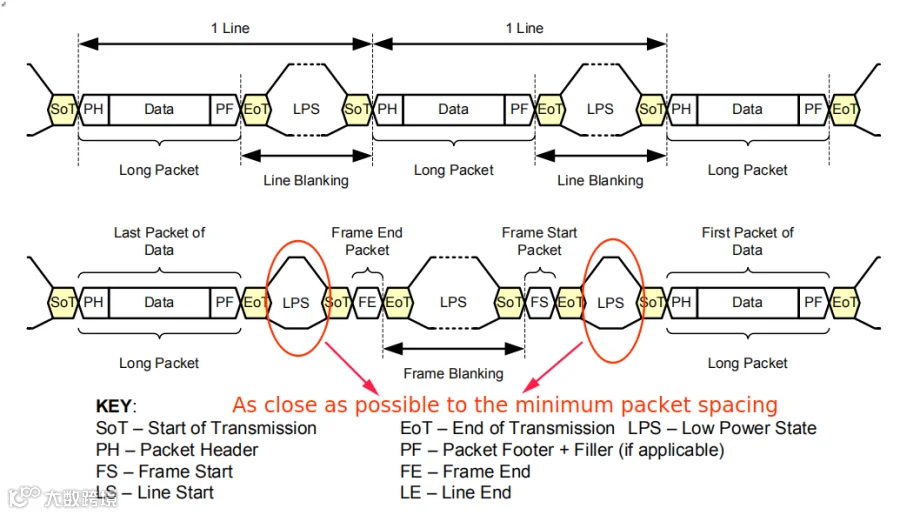

从上图也可以看到,从LLP封包Checksum、EoT、LPS、SOT,一直到 PH,正好处于行同步信号为低,这段区间就是每行的Blanking区间。

长包EoF,下一个长包SoF,以及之间的LPS称之为Line Blanking;帧尾(FE)后的EoT,下一帧帧头(FS)前的SoT,以及之间的LPS称之为Frame Blanking。

再从行同步和帧同步的角度,来看看帧尾和帧头之间的LPS(VSYNC区域),即Frame Blanking,以及行尾行头之间的Line Blanking,会更加容易理解。

Frame and

Line Synchronization Packets

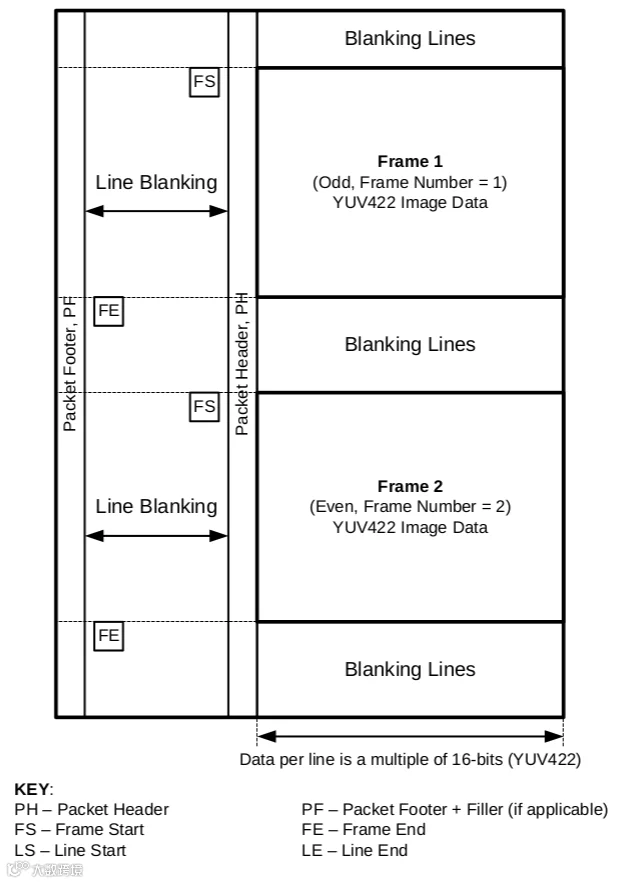

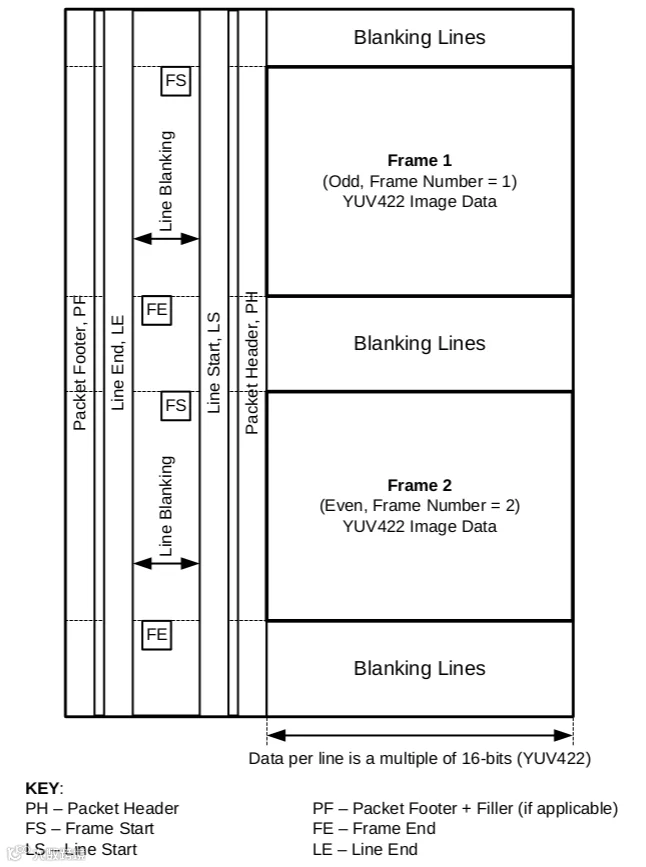

帧头(FS)帧尾(FE)之间至少包含1~n个图像数据长包,0~n个代表同步讯号的短包,也就是说行头(SoT)行尾(EoT)的短包是可以省略的。

YUV、RGB和RAW数据的每一个长包包含1行图像数据。

通用帧格式实例如下,行头(SoT)行尾(EoT)的短包被省略,且帧头(FS)和第一个长包,以及最后一个长包和帧尾(FE)之间的LPS要尽可能的短,如下画圈部分。

精确同步的数字隔行视频格式实例如下,未省略行头行尾的短包。

如下为高速模式下数据和时钟的关系图,可以清楚地了解到高低速序号,LPS的转变过程。

数据交错(Data Interleaving)主要有两种方式:1. 通过DT区分;2. 通过VC区分。

所有的包使用同一VC,然后独立的DT,共享帧头(FS)帧尾(FE)和行头(SoT)行尾(EoT),如下:

Virtual Channel Identifier Interleaving

每一个VC拥有自己的帧头(FS)和帧尾(FE),而且每一个VC还可以继续通过DT来扩展数据通路。

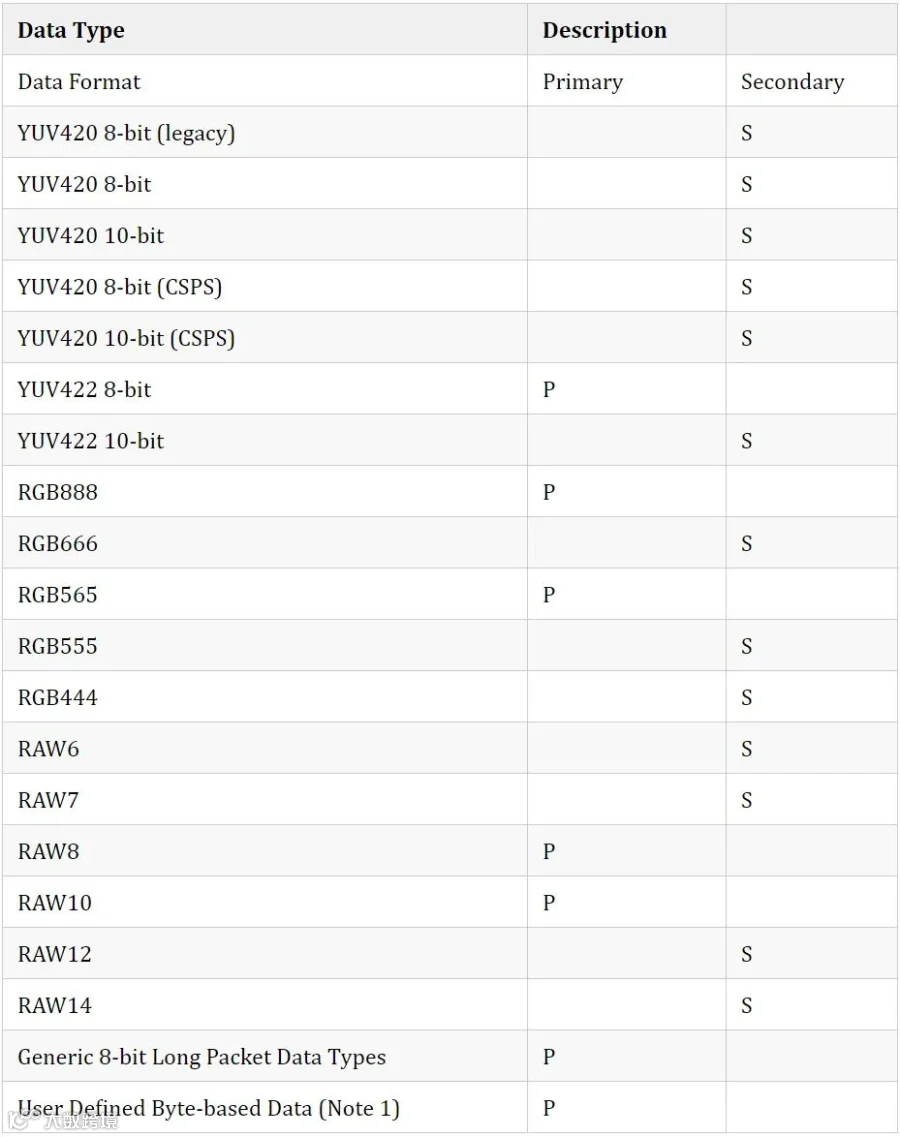

Primary代表广泛采用的数据格式,MIPI联盟规定发送端需要支持至少一个 primary格式,接收端需要支持所有的Primary数据格式。

Reference:

Specification for Camera Serial Interface 2 (CSI-2)

牛芯半导体(深圳)有限公司(简称“牛芯半导体”)成立于2020年,聚焦接口IP的开发和授权,并提供相关整体解决方案,致力成为全球领先的IP供应商。

基于自主可控的核心技术,牛芯半导体在主流先进工艺布局SerDes、DDR等中高端接口IP,产品广泛应用于消费电子、网络通信、数据存储、人工智能、汽车电子、医疗电子等领域。

未来,牛芯半导体持续响应IP国产化需求,适应不断演进的接口技术和日益拓展的接口互联场景,赋能数智时代下的千行百业。