本文转载自系统级SIPI设计与仿真,转载文章仅供学习和研究使用。

为什么需要GDDR6?

市场和客户对GDDR6的需求

-

目标带宽为GDDR5的2倍: 每设备最高64GB/s(32个I/O,16Gb/s/引脚,数据速率相对GDDR5提升2倍)。

-

支持细粒度内存访问(对图形应用性能至关重要)。 -

沿用类似BGA封装布局与引脚排列,便于利用现有PCB布线及信号分析经验。 -

测量与仿真相关性需迭代优化。

GDDR6接口简介

-

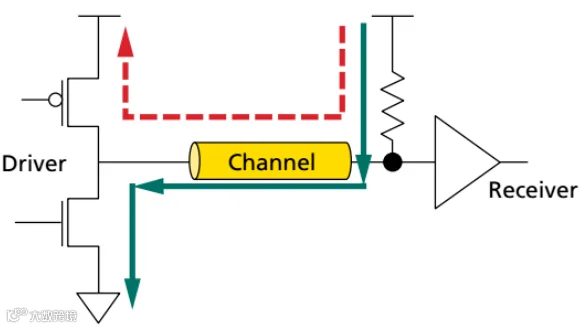

GDDR6专注优化点对点配置。从SI角度考虑,由于单端速率达到16Gbps,所以不支持DIMM形式以及多Rank(一驱多拓扑,恶化SI性能)设计。

-

所有高速I/O(CK、WCK、CA、DQ/DBI)都支持片上端接(ODT)。 -

WCK替代DDR DRAM的DQS,读写数据以WCK_t/WCK_c为参考,采用DDR模式。

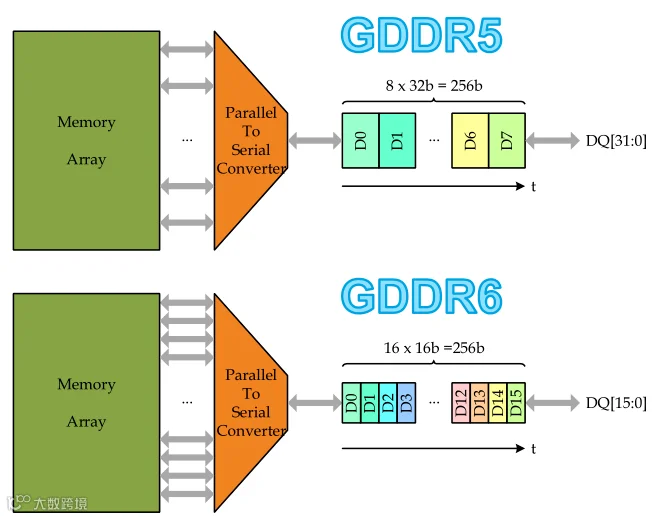

DRAM核心架构/阵列预取

-

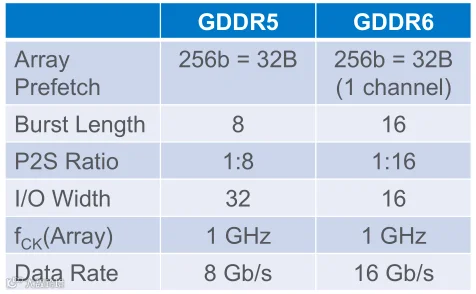

增加阵列预取是扩展性能最具成本效益的方式。下表为GDDR6和GDDR5的阵列预存取参数对比:

-

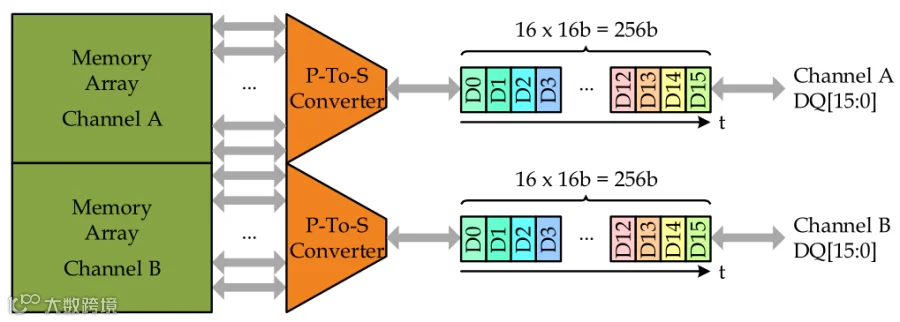

GDDR6将32位I/O接口分为两个16位逻辑通道(通道A/B独立运行),单个通道的预存取阵列与32bit的GDDR5相同。

-

GDDR6的burst长度16也是GDDR5的两倍。并串转换的比例1:16也是GDDR5的两倍,在相同的fck(Array)时钟频率下实现了data rate的翻倍。

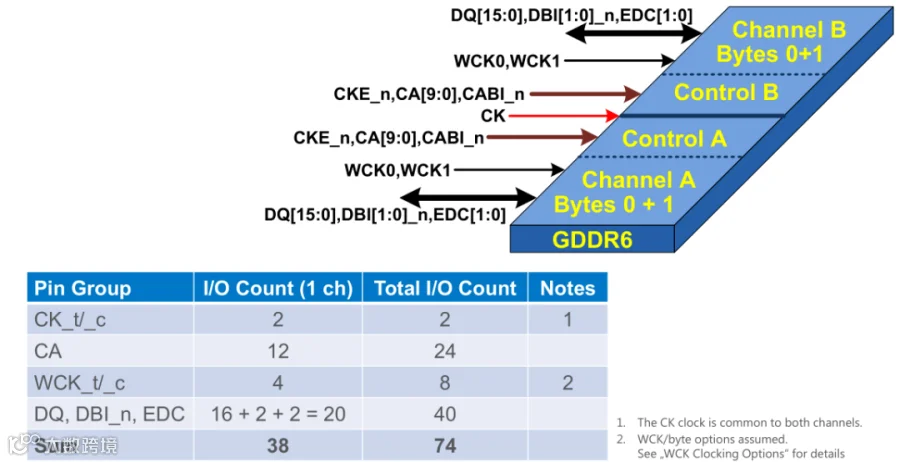

GDDR6引脚数量

-

总I/O数:74(包含CK、CA、WCK、DQ/DBI/EDC等)。 CK时钟为双通道共用,WCK按byte配置。

-

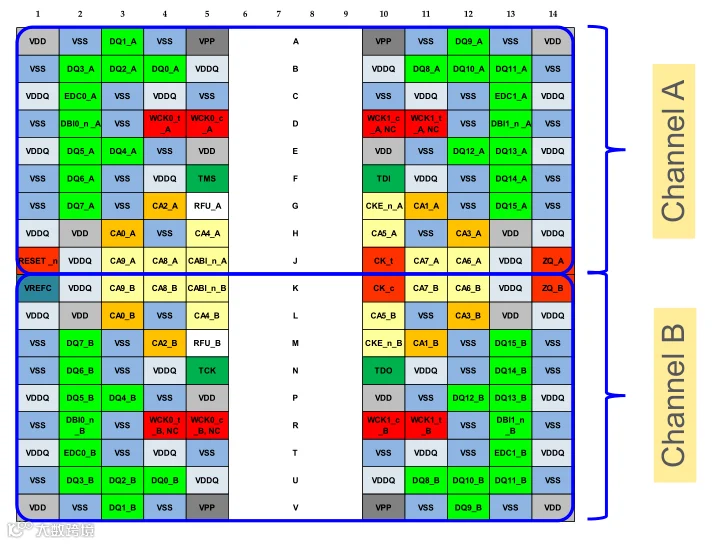

GDDR6的ball排布: 对称设计,每象限分配一个数据字节,方便PCB布线。

水平镜像轴位于J行与K行之间。共用信号:RESET_n、VREFC、JTAG。 共用信号:RESET_n、VREFC、JTAG。 两个channel共用时钟,可以在相同频率下独立运行。

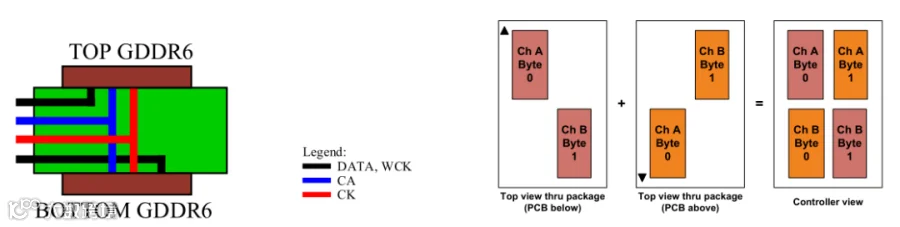

Clamshell模式设计实现更高内存容量

-

两颗GDDR6可配置为Clamshell模式,对Controller显示为密度翻倍的单一设备。 -

两颗GDDR6对贴在一起增加了高速DQ信号的过孔和布线密度。需在GDDR6的PCBfanout设计时做一些调整。CA信号为一驱二拓扑,高速DQ、WCK信号信号保持点对点拓扑。 -

对称的ball排布使Clamshell模式成为可能。 -

在启动时配置Clamshell模式。

总线反转(DBI/CABI)

-

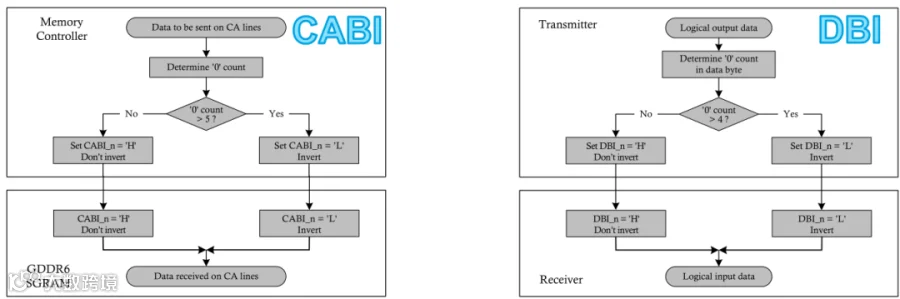

POD I/O系统仅在信号为低电平时消耗静态电流。

-

CABI(CA总线反转)与DBI(数据总线反转)限制电流的消耗与di/dt: CABI规则:当CA总线超过5位为低时反转信号。 DBI规则:当每字节数据超过4位为低时反转信号。

-

DBI必须启用,CABI强烈建议启用。

数据链路保护(CRC)

-

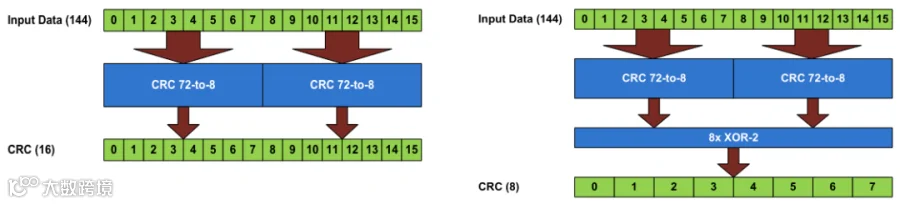

沿用GDDR5的CRC多项式,支持全速率与半速率校验: 全速率CRC:16位校验,覆盖100%单/双/三比特错误。两个连接的8位校验和,由BL16突发的第一部分(UI 0到7)和第二部分(UI 8到15)分别计算得出。 半速率CRC:8位校验,能够覆盖100%随机单比特、双比特,99.6%的三比特和四比特失败。两个8位中间校验和进行异或运算得到一个8位校验和。未显示存在额外的逻辑可防止两个中间校验和之间出现别名错误。

数据接收器参考电压

-

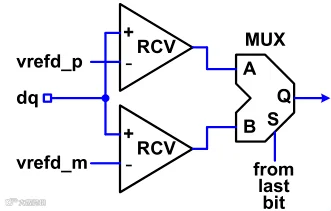

步长0.005*VDDQ(6.75mV)。 -

大范围:0.49*VDDQ到0.965*VDDQ。 -

适用于48Ω/40Ω和60Ω/40Ω。 -

Per-pin和per-byte选择:Per-byte更快,执行更少的MRS命令。

往期推荐

|

|||

|

|||

|

牛芯半导体(深圳)有限公司(简称“牛芯半导体”)成立于2020年,聚焦接口IP的开发和授权,并提供相关整体解决方案,致力成为全球领先的IP供应商。

牛芯半导体在主流先进工艺布局SerDes、DDR等中高端接口IP,产品广泛应用于消费电子、网络通信、数据存储、人工智能、汽车电子、医疗电子等领域。

未来,牛芯半导体持续响应IP市场需求,适应不断演进的接口技术和日益拓展的接口互联场景,赋能数智时代下的千行百业。