本文转载自CSDN论坛作者WangAnChuan0033的博客,转载文章仅供学习和研究使用。

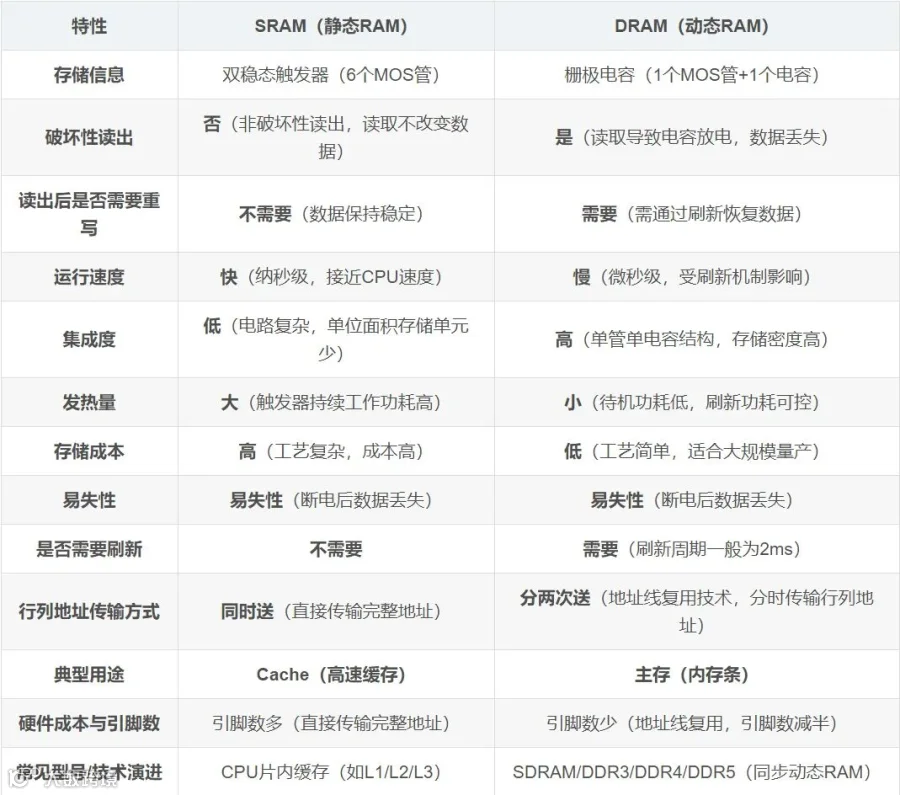

SRAM与DRAM的核心区别

DRAM的刷新机制与技术实现

-

刷新计数器:独立于CPU的计数器,按行地址递增顺序自动生成刷新地址。 -

刷新仲裁器:协调正常读写请求与刷新操作,确保刷新在2ms内完成且不影响关键操作。 -

自刷新模式(Self-Refresh):低功耗场景下(如笔记本待机),内存控制器进入休眠,由内存芯片内部电路独立完成刷新。

DRAM的地址复用技术与引脚优化

-

减少引脚数的公式推导:假设存储容量为(2^n)位,传统SRAM需n根地址线;DRAM采用行列地址复用后,地址线数减少为(n/2)根(假设行地址=列地址=(n/2)位)。

例:1Gb((2{30})位)DRAM.若存储矩阵为(2{15}×2^{15})(行×列),则地址线数=15根(行)+15根(列)→复用后仅需15根地址线(分时传输)。

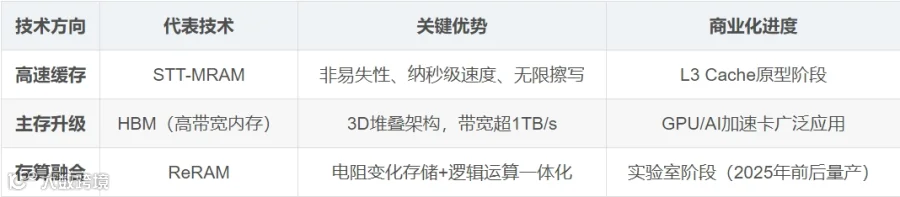

SRAM与DRAM的演进技术与应用生态

-

从片外到片内的集成: 早期CPU(如80386)采用片外SRAM作为Cache,通过高速总线连接。 现代CPU(如Intel i7)将L1/L2/L3 Cache全部集成在芯片内,L3 Cache容量可达30MB以上,采用FinFET工艺提升密度。 -

新兴应用场景: 神经网络加速器(如NPU)的权重缓存,利用SRAM的高速特性加速矩阵运算。 FPGA内部的Block RAM,用于存储可编程逻辑的配置数据和临时计算结果。

-

ZNS SSD(Zone-Named Storage):结合DRAM缓存与QLC闪存,DRAM用于存储FTL(闪存转换层)映射表,提升大文件顺序写入性能。 -

存算一体架构(Processing-in-Memory, PIM):在DRAM芯片内集成计算单元,减少数据搬运功耗(如三星PIM芯片,能效比提升10倍以上)。

未来技术展望与存储生态变革

-

3D SRAM:通过堆叠多层晶体管(如Intel 3D XPoint),在不缩小制程的前提下提升存储密度。 -

铁电DRAM(FeDRAM):利用铁电晶体的极化特性存储数据,兼具SRAM速度与DRAM密度,预计2026年量产。

总结

往期推荐

|

|||

|

|||

|

牛芯半导体(深圳)有限公司(简称“牛芯半导体”)成立于2020年,聚焦接口IP的开发和授权,并提供相关整体解决方案,致力成为全球领先的IP供应商。

牛芯半导体在主流先进工艺布局SerDes、DDR等中高端接口IP,产品广泛应用于消费电子、网络通信、数据存储、人工智能、汽车电子、医疗电子等领域。

未来,牛芯半导体持续响应IP市场需求,适应不断演进的接口技术和日益拓展的接口互联场景,赋能数智时代下的千行百业。