本文转载自系统级SIPI设计与仿真,转载文章仅供学习和研究使用。

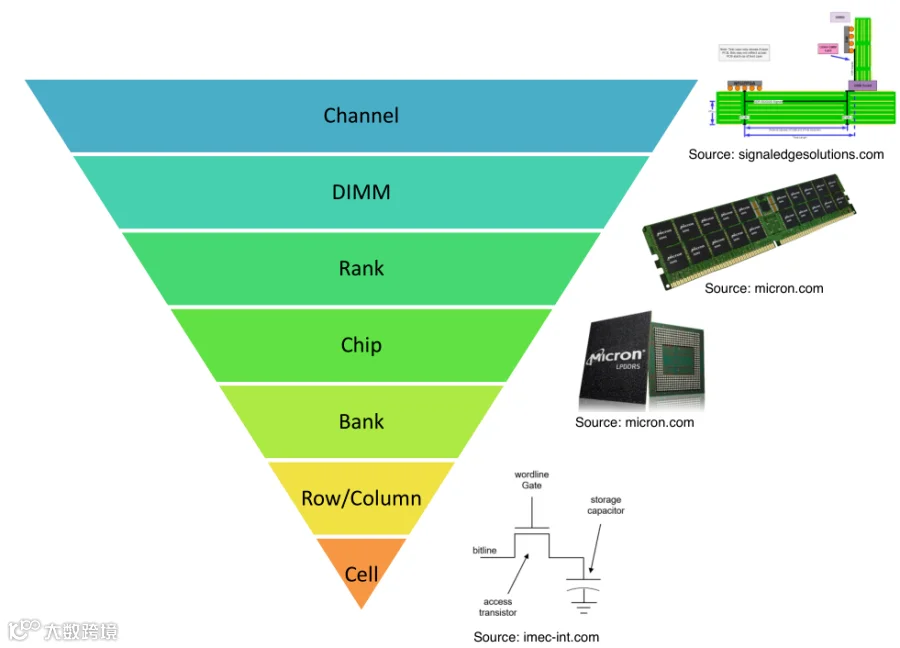

DRAM内存架构

-

Cell(存储单元):是内存的最基本存储单元,由电容器和晶体管组成。工作原理是利用电容器存储电荷来表示数据,电荷的存在与否分别对应逻辑“1”和“0”。但由于电容器存在漏电现象,DRAM需要定期刷新以保持数据。其结构有平面、沟槽和堆叠式电容器等类型,不同结构在性能、集成度上各有优劣,比如堆叠式电容器能提高存储密度。

-

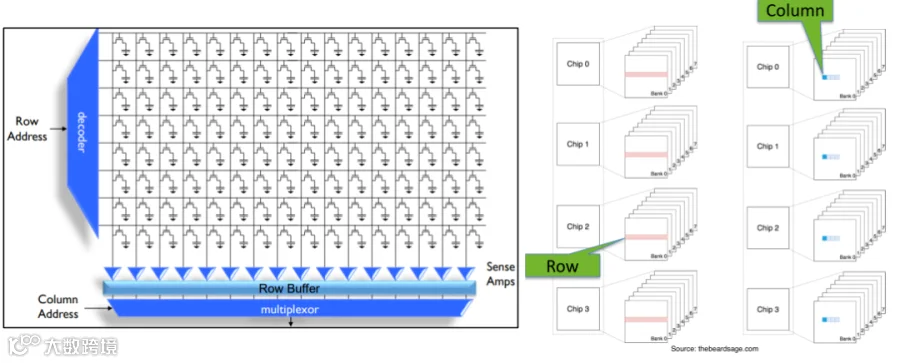

Row/Column(行/列):多个存储单元按行和列的形式排列组成存储阵列。行是一组能被同时激活的存储单元,当接收到行激活命令,一行的存储单元会并行工作。列是可独立进行读写操作的最小单元,通过列地址选通(CAS)信号来选择特定列进行数据传输。在进行内存读写时,先通过行地址选通(RAS)信号选中某一行,再用CAS信号选择列,从而定位到具体存储单元进行数据操作。

-

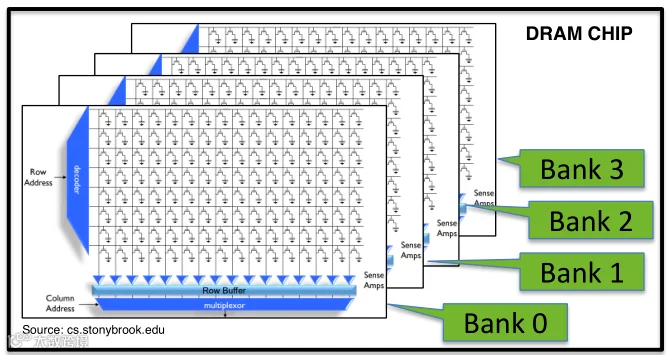

Bank:是DRAM芯片内独立的存储阵列分区,由多个行和列组成。一般的DRAM芯片包含4、8、16个甚至更多bank,随着内存密度提升,bank数量会增加,像DDR5 x4/x8设备中,16Gb内存就有32个bank。bank可独立进行读写操作,能并行处理不同的内存请求,提升内存整体性能,比如在多任务处理时,不同任务的数据可分别在不同bank中读写。

-

Chip(芯片):由多个存储体、行/列译码器、数据缓冲器等组成。多个存储体协同工作,通过行/列译码器选择具体的行和列,数据缓冲器负责数据的暂存和传输。不同类型的内存芯片在容量、速度等性能指标上有差异,如GDDR6芯片更注重高带宽,适用于图形处理,而LPDDR系列芯片侧重低功耗,用于移动设备。 -

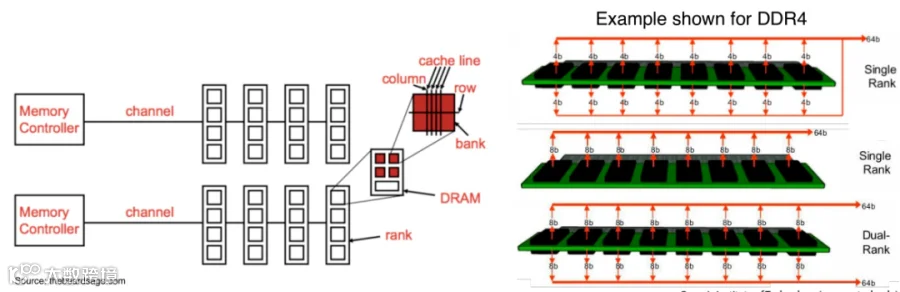

Rank:是内存模块中一组协同工作的DRAM芯片集合,同一Rank内的芯片共享地址和命令总线,但各自提供不同的数据位。以DDR4为例,常见的单Rank包含8个或9个DRAM芯片(9个芯片时含1个用于ECC校验,64 bits of data + 8 bits ECC),这些芯片同时被控制,通过芯片选择(CS_n)信号来确定对哪个Rank进行操作。 下图右图为三个64bit位宽的内存条:(上)用x4的DDR颗粒,正反对贴的16个颗粒组成64bit的单rank内存接口;(中)使用x8的DDR颗粒,8个颗粒组成64bit的单rank内存接口;(下)16个x8的DDR颗粒组成双rank内存接口,需要通过CS_n片选对相应rank进行操作。

-

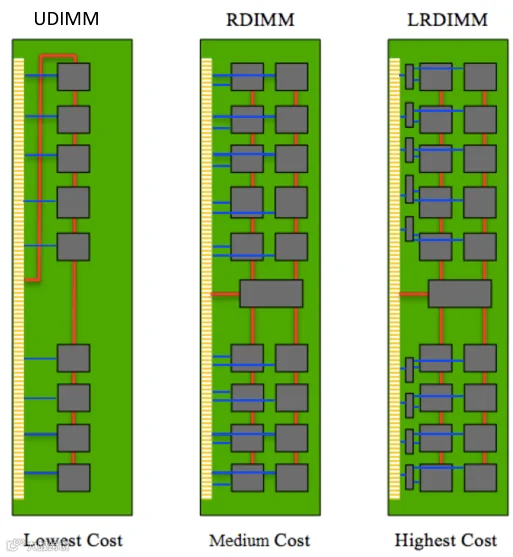

DIMM(双列直插式内存模块):将多个Rank的芯片集成在一块印刷电路板上形成DIMM(也就是我们通常所说的内存条)。常见的有UDIMM(无缓冲双列直插式内存模块)、RDIMM(寄存器缓冲双列直插式内存模块)和LRDIMM(负载降低缓冲数据双列直插式内存模块)。不同类型的DIMM在功能和适用场景上有区别,UDIMM成本低但负载能力有限;RDIMM和LRDIMM适用于高容量、高数据速率系统,能降低信号干扰,但会增加系统成本、延迟和功耗。 DDR3和DDR4支持三种主要DIMM类型: 无缓冲DIMM(UDIMM):CK、C/A信号负载数量多,SI设计难度大。 RDIMM:用于CK、ADDR、CMD、CTRL网络带寄存器缓冲,有效降低负载数量,降低SI设计难度。 LRDIMM:除了CK、ADDR、CMD、CTRL网络,DQ网络也带有减载缓冲,降低多rank内存条中DQ信号SI设计难度。

-

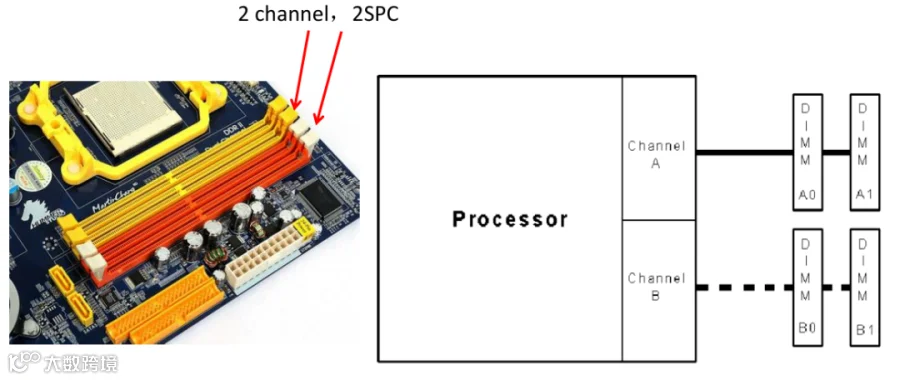

Channel:是内存控制器与DIMM之间的数据传输通路。一个内存控制器可连接多个通道,如常见的双通道、四通道技术。每个通道可独立传输数据,增加通道数量能提升内存带宽,提高数据传输效率。在多通道系统中,内存控制器会根据负载情况合理分配数据到不同通道,实现并行传输,提升系统整体性能。

往期推荐

|

|||

|

|||

|

牛芯半导体(深圳)有限公司(简称“牛芯半导体”)成立于2020年,聚焦接口IP的开发和授权,并提供相关整体解决方案,致力成为全球领先的IP供应商。

牛芯半导体在主流先进工艺布局SerDes、DDR等中高端接口IP,产品广泛应用于消费电子、网络通信、数据存储、人工智能、汽车电子、医疗电子等领域。

未来,牛芯半导体持续响应IP市场需求,适应不断演进的接口技术和日益拓展的接口互联场景,赋能数智时代下的千行百业。