本文转载自CSDN论坛作者G2突破手259的博客,转载文章仅供学习和研究使用。

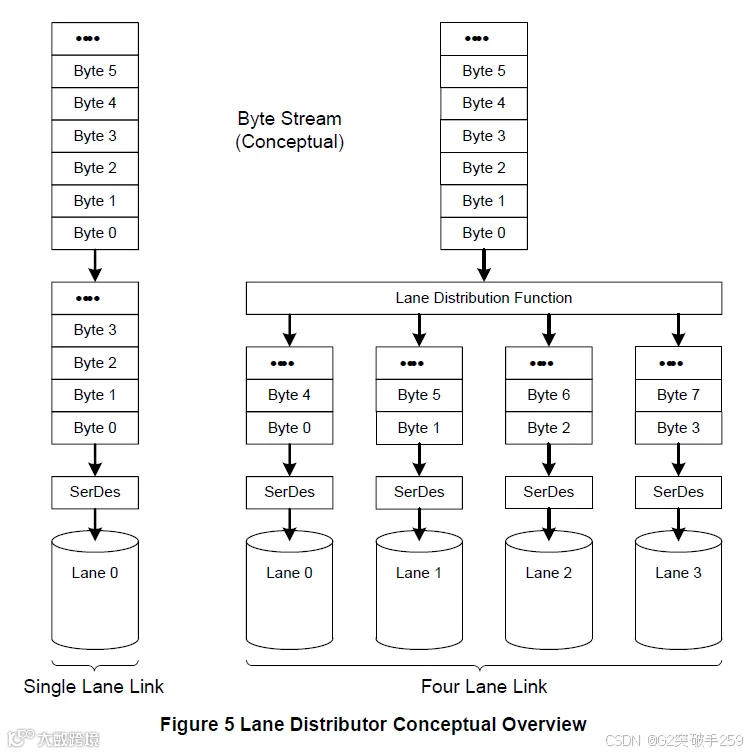

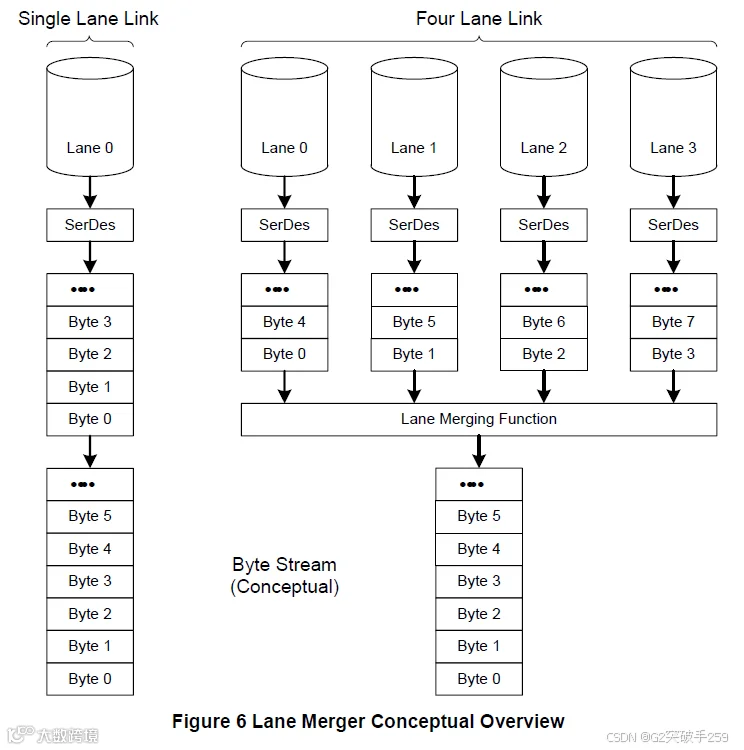

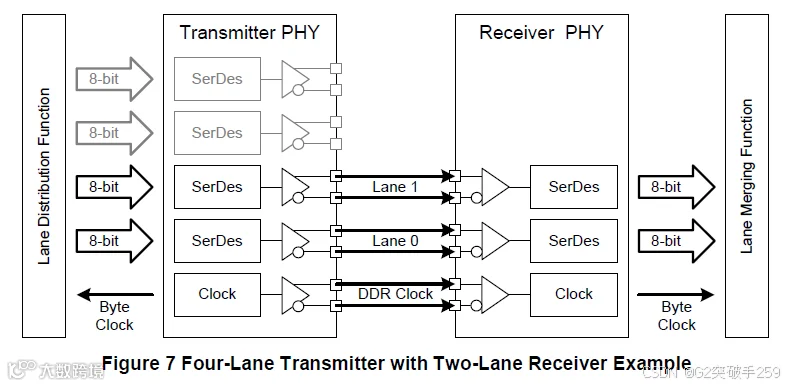

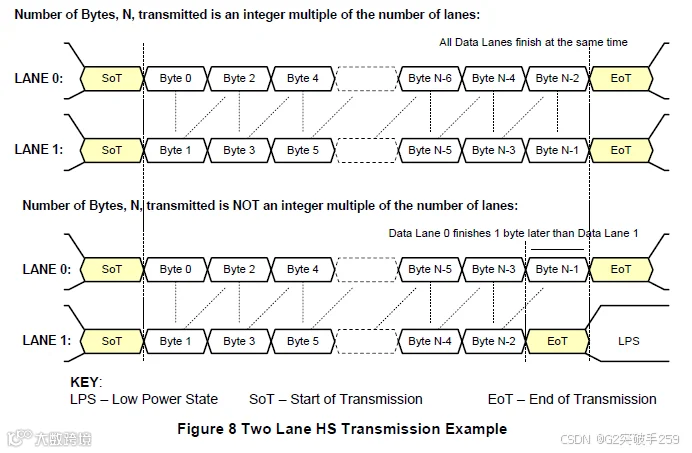

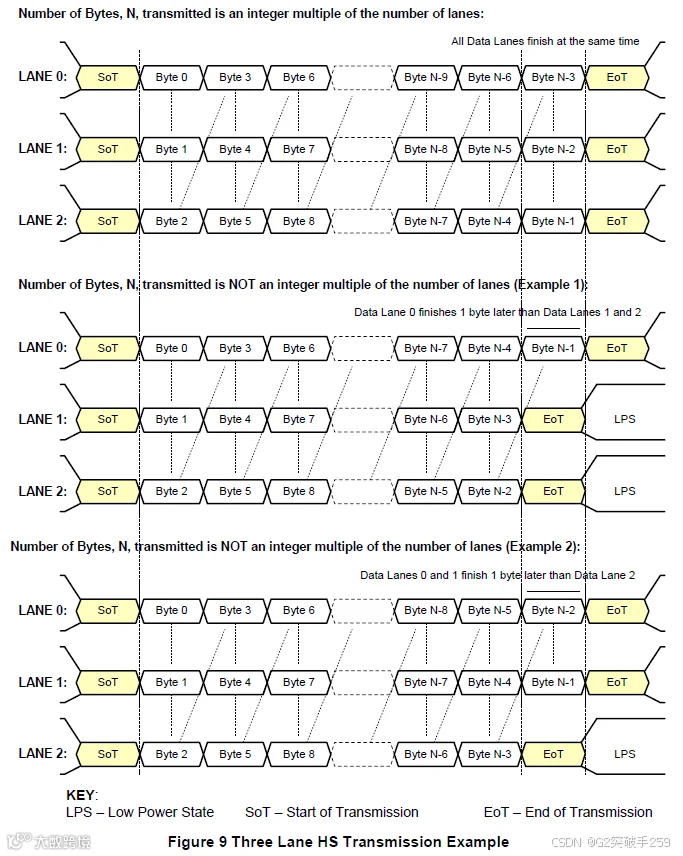

多通道分配与合并

底层协议错误和竞争

-

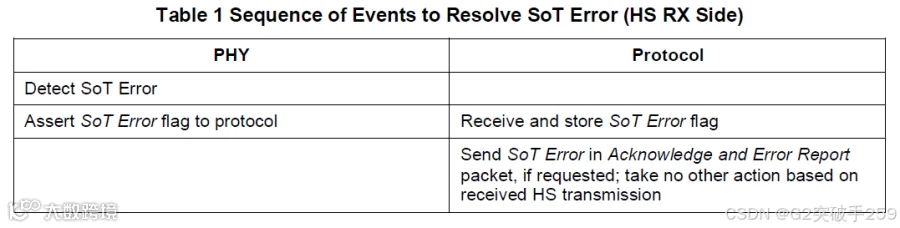

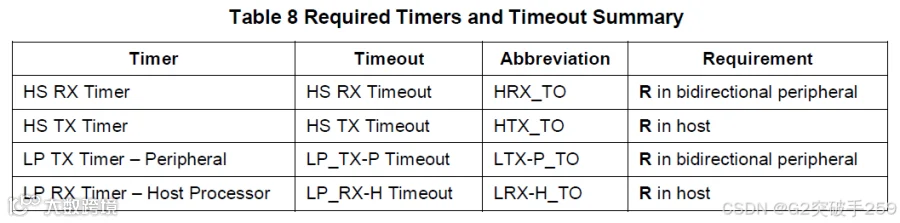

SoT Error 高速开始传输(SoT)的前导序列对任何单比特错误和一些多比特错误都具有容错性。因此,如果检测到错误,接收到的同步位和随后的数据包可能仍然没有损坏,但对有效负载数据完整性的信心较低。此条件应与带有 SoT错误标志的协议通信。

外设PHY检测到SoT错误。如果期望得到确认响应,外设将使用数据类型 0x02(确认和错误报告)发送响应,并在返回包中设置SoT错误位给主机处理器。外围设备不应该根据收到的可能损坏的HS传输采取其他操作。 -

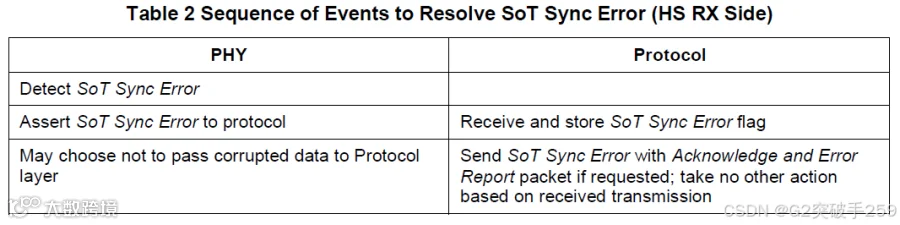

SoT Sync Error 如果SoT前导序列被损坏,不能期望正确的同步,SoT同步错误将被标记。HS传输中的后续数据可能已损坏,不应使用。

外设PHY检测到SoT同步错误。如果期望得到确认响应,外设将使用数据类型 0x02(确认和错误报告)发送响应,并在返回包中设置SoT同步错误位给主机处理器。由于数据可能已损坏,因此在外设中不应解释或操作任何命令。不得在外围设备中进行写操作。 -

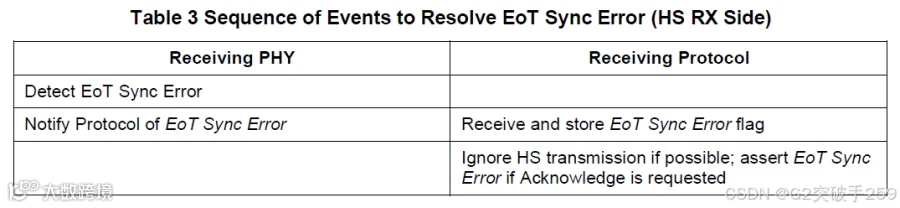

EoT Sync Error DSI是一种面向字节的协议。所有未损坏的HS传输都包含整数字节。如果,在EoT序列期间,外设PHY检测到最后一个字节不匹配字节边界,EoT 同步错误将被标记。如果期望得到一个确认响应,外围设备将发送一个确认和错误报告包。外设应该在返回给主机处理器的包的错误报告字节中设置EoT同步错误位。 如果可能,外设应该不采取任何动作,尤其是WRITE活动,以响应预期的命令。由于此错误直到包的末尾才被识别,因此在检测到错误之前可能会发生一些不可逆的操作。

-

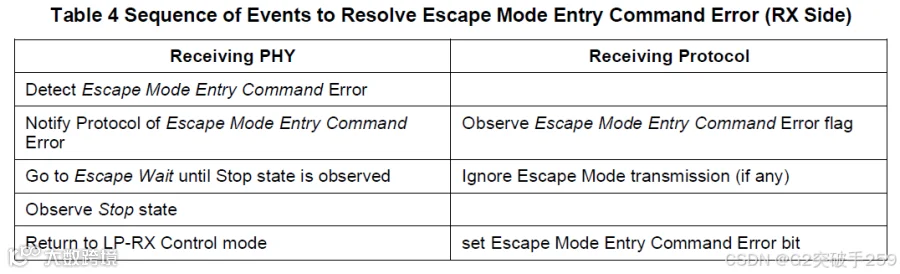

Escape Mode Entry Command Error 如果链路开始一个Escape模式序列,但是Escape模式进入命令不能被接收的PHY Lane识别,接收方应该标记Escape模式进入命令错误。从发送方的角度来看,这种情况可能是一个合法的命令,但接收协议无法识别或理解它。在双向系统中,链路两端的接收器应检测和标记无法识别的Escape模式序列。只有外设会报告这个错误。

-

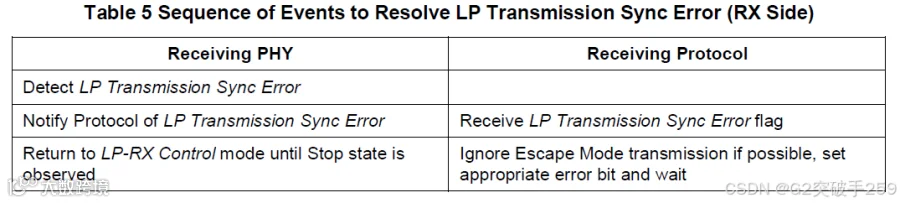

LP Transmission Sync Error 如果在低功耗传输结束时接收的数据未同步到字节边界,则断言此错误标志。在双向系统中,链路两端的接收器应检测并标记LP传输同步错误。只有外设会报告这个错误。

-

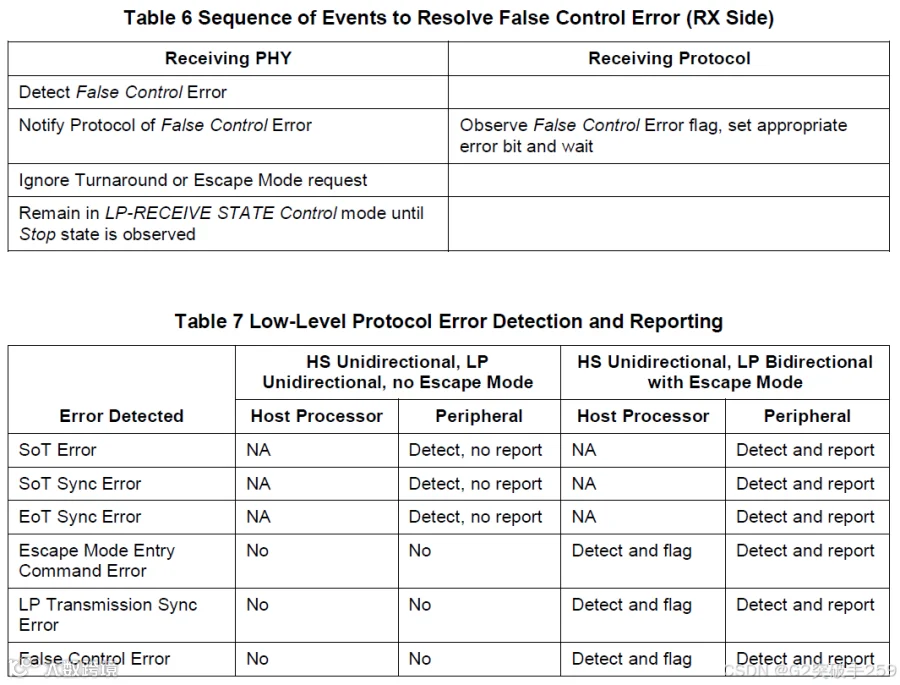

False Control Error 如果外设检测到LP-10(LP请求)之后没有剩余的有效Escape或反转序列,或者如果检测到LP-01(HS请求)之后没有桥接状态(LP-00),则在错误状态寄存器中捕获一个假控制错误,并在下一个BTA之后报告给主机。此错误应该在本地标记到接收协议层,例如,当主机检测LP-10没有遵循有效的Escape或反转序列的剩余部分时。

往期推荐

|

|||

|

|||

|

牛芯半导体(深圳)有限公司(简称“牛芯半导体”)成立于2020年,聚焦接口IP的开发和授权,并提供相关整体解决方案,致力成为全球领先的IP供应商。

牛芯半导体在主流先进工艺布局SerDes、DDR等中高端接口IP,产品广泛应用于消费电子、网络通信、数据存储、人工智能、汽车电子、医疗电子等领域。

未来,牛芯半导体持续响应IP市场需求,适应不断演进的接口技术和日益拓展的接口互联场景,赋能数智时代下的千行百业。