本文转载自CSDN论坛作者Hug Freedom.的博客,转载文章仅供学习和研究使用。

-

PCIe:即PCIe基础规范中的协议。 -

CXL:源自CXL规范,但不支持RCD/RCH/eRCD/eRCH。 -

流协议:为用户自定义协议提供通用传输模式,方便各类自定义协议借助 UCIe传输数据。 每种协议在UCIe上传输时,都有不同的优化方式和数据单元(Flit)传输规则。

UCIe Configurations

-

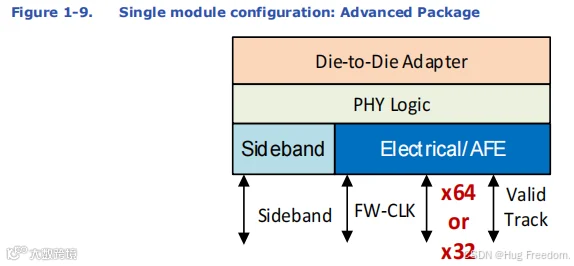

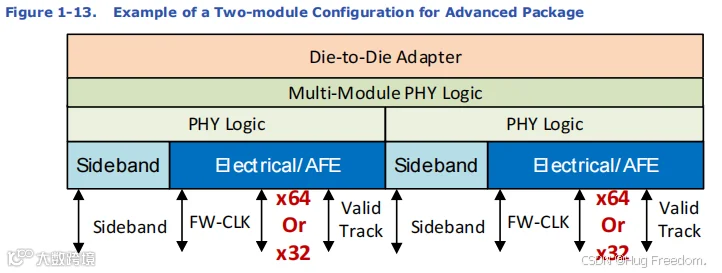

高级封装:单模块配置是一个x64或x32的数据接口,就像一条有64或32 条“车道”的数据通道。

-

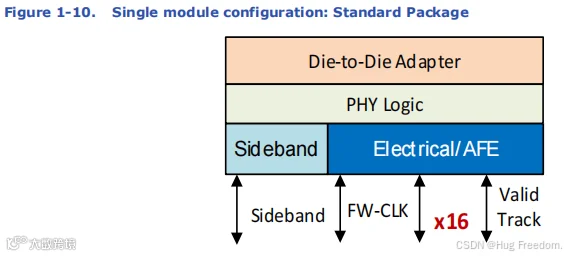

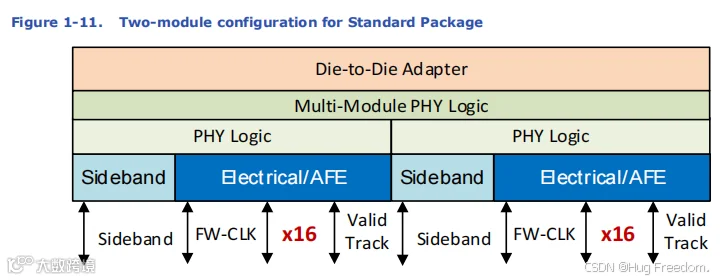

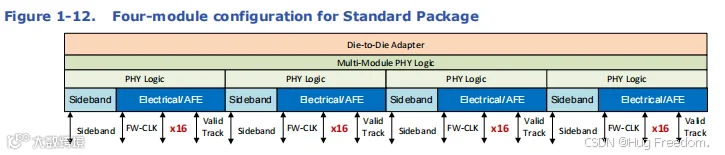

标准封装:单模块配置是一个x16的数据接口,即数据通道有16条“车道”。

-

多实例独立运行:如果有多个单模块配置的实例,且每个模块都有自己专用的适配器(Die - to - Die Adapter),它们可以独立运行。例如,不同模块可以以不同的数据速率和宽度传输数据,就像多条独立的道路,每辆车(数据)的行驶速度(速率)和车道数量(宽度)可以不同。

-

配置类型:规范允许两模块和四模块配置。 -

共同适配器下的要求:当这些模块使用一个共同的适配器时,两模块和四模块配置中的模块必须以相同的数据速率和宽度运行。例如,两模块配置就像两条并行的道路,每辆车的行驶速度和车道数量必须一致;四模块配置同理。

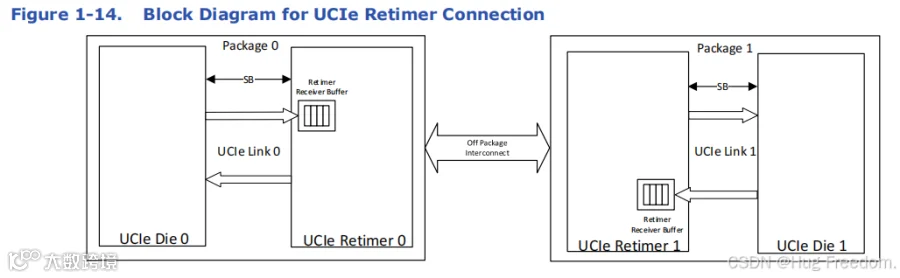

UCIe Retimers

-

随着链路速度(4 GT/s 至 32 GT/s)提升,高级封装(x64)和标准封装的带宽密度均增加。例如,4 GT/s时,高级封装为165 GB/s per mm,标准封装为 28 GB/s per mm;32 GT/s时,高级封装达1317 GB/s per mm,标准封装为224 GB/s per mm。 -

高级封装的带宽密度显著高于标准封装,体现其更强的高速数据传输能力。

-

0.7 V供电电压: 高级封装:≤12 GT/s时为0.5 pJ/bit,≥16 GT/s时为0.6 pJ/bit。 标准封装:≤16 GT/s时为1.0 pJ/bit,32 GT/s时为1.25 pJ/bit。 -

0.5 V供电电压: 高级封装:≤12 GT/s时为0.25 pJ/bit,≥16 GT/s时为0.3 pJ/bit。 标准封装:≤16 GT/s 时为 0.5 pJ/bit,32 GT/s 时为 0.75 pJ/bit。

-

芯片边缘带宽密度的定义与凸点间距有关(高级封装45 - um,标准封装 110 - um),x32高级封装模块的带宽密度是x64的50%。 -

能效计算包含适配器和物理层相关电路(如发送、接收、锁相环、时钟分配等)的能耗。

-

延迟包含发送和接收方向上适配器和物理层的延迟。

Interoperability

-

互操作的基本要求:封装设计者需确保同一封装上连接的芯片(Dies)能够互操作,这涉及兼容的封装互连(如高级封装与标准封装的差异)、协议、电压水平等。强烈建议芯片采用低于0.85 V的发射极电压,以便在未来可预见的时间内,能与广泛的工艺节点实现互操作。 -

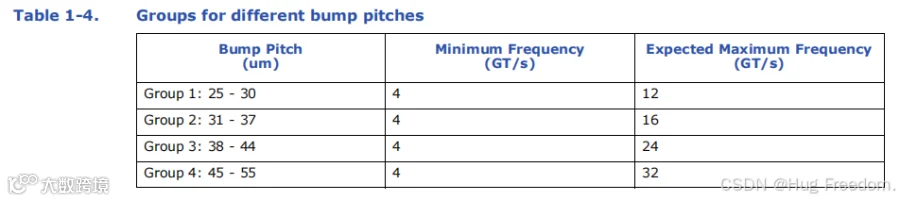

高级封装的凸点间距与互操作性:该规范涵盖了高级封装选项中广泛的凸点间距(bump pitch)的互操作性。随着时间推移,预计更小的凸点间距将成为主流。采用更小凸点间距时,设计会降低最大宣传频率(即便可达到32G),以优化面积,并应对高带宽下因面积减小带来的电源传输和热约束问题。 -

性能目标的凸点间距基础:表中的性能目标基于45-um凸点间距,这是依据UCIe 1.0和UCIe 1.1规范发布时(2022-2023年)广泛部署的技术确定的。

往期推荐

|

|||

|

|||

|

牛芯半导体(深圳)有限公司(简称“牛芯半导体”)成立于2020年,聚焦接口IP的开发和授权,并提供相关整体解决方案,致力成为全球领先的IP供应商。

牛芯半导体在主流先进工艺布局SerDes、DDR等中高端接口IP,产品广泛应用于消费电子、网络通信、数据存储、人工智能、汽车电子、医疗电子等领域。

未来,牛芯半导体持续响应IP市场需求,适应不断演进的接口技术和日益拓展的接口互联场景,赋能数智时代下的千行百业。