本文转载自CSDN论坛作者主公讲 ARM的博客,转载文章仅供学习和研究使用。

DDR中的通道(Channel)概念

-

通道是CPU与内存之间的独立数据传输路径,每个通道包含完整的信号线(数据线、地址线、控制线)。 -

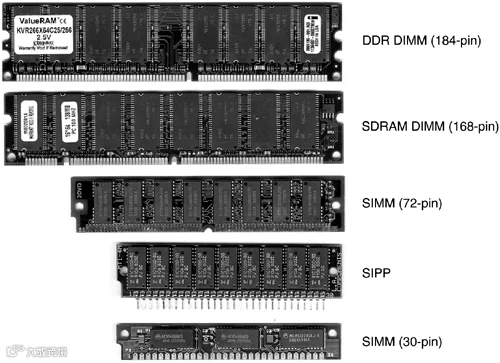

位宽:每个通道的位宽通常为64位(现代DDR标准),双通道则为128位,以此类推。 -

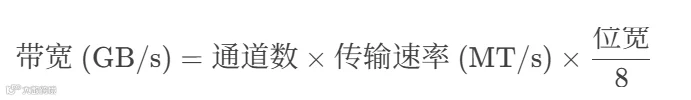

带宽公式:

-

并行性:多个通道可同时传输数据,提升带宽和效率。 -

独立性:每个通道可独立操作不同内存颗粒(如双通道操作两个DIMM),减少访问冲突。 -

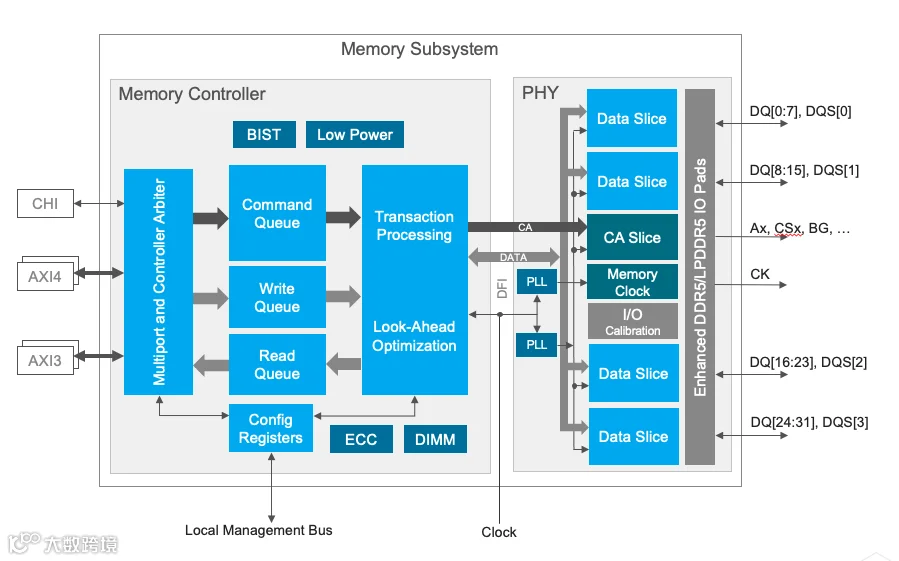

信号线分配:每个通道需独立的。 -

数据线(DQ):传输实际数据。 -

地址/命令线(CA):传输行地址(Row)、列地址(Column)、命令(Activate/Read/Write等)。 -

时钟(CLK):同步信号。

-

单channel:由64个DQ、1个clk、1个Ma、1个Dqs组成。 -

双channel:由128个DQ、2个clk、2个Ma、2个Dqs组成。 -

四channel:由256个DQ、4个clk、4个Ma、4个Dqs组成。

-

单channel:由64个DQ、1个clk、1个Ma、1个Dqs组成。 -

双channel:由128个DQ、2个clk、2个Ma、2个Dqs组成。 -

四channel:由256个DQ、4个clk、4个Ma、4个Dqs组成。

-

数据线(DQ):传输实际数据。 -

地址/命令线(CA):传输行地址(Row)、列地址(Column)、命令(Activate/Read/Write等)。 -

数据传输频率时钟(CLK):同步信号。

-

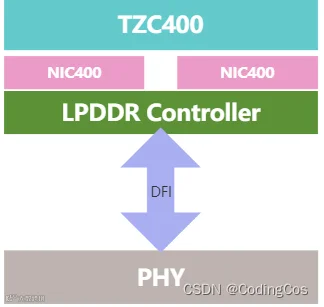

地址映射决定通道路由:CPU发出的物理地址通过高位地址(如A[31:28])选择目标DDR控制器和通道。

-

A[31]=0 → Channel 0(地址范围0x0000_0000–0x7FFF_FFFF) -

A[31]=1 → Channel 1(地址范围0x8000_0000–0xFFFF_FFFF) -

多核并行访问:不同核心访问不同地址时,CI-700根据地址的高位将请求路由到不同的DDR控制器,实现通道级并行。

往期推荐

|

|||

|

|||

|

牛芯半导体(深圳)有限公司(简称“牛芯半导体”)成立于2020年,聚焦接口IP的开发和授权,并提供相关整体解决方案,致力成为全球领先的IP供应商。

牛芯半导体在主流先进工艺布局SerDes、DDR等中高端接口IP,产品广泛应用于消费电子、网络通信、数据存储、人工智能、汽车电子、医疗电子等领域。

未来,牛芯半导体持续响应IP市场需求,适应不断演进的接口技术和日益拓展的接口互联场景,赋能数智时代下的千行百业。