本文转载自eKnow AI,转载文章仅供学习和研究使用。

高频损耗与阻抗匹配创新

-

混合键合技术:UCIe-3D采用铜-铜键合(Cu-Cu),寄生电阻/电容降低90%,带宽密度提升至300TB/s/mm²(1μm间距),同时功耗密度降至0.3pJ/bit。 -

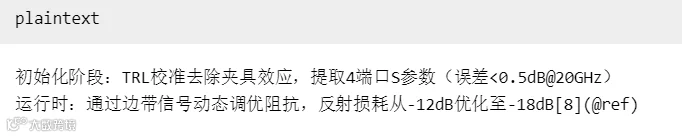

动态阻抗匹配:传统静态匹配电路增加静态功耗,UCIe-3D PHY采用按需校准技术:

串扰抑制与通道优化

-

三维屏蔽结构:在硅中介层RDL层插入接地过孔阵列(间距50μm),将NEXT从-28dB降至-38dB。 -

中继器插入策略:针对>10mm长距通道,插入低功耗中继器(功耗<0.5pJ/bit),插入损耗从-22dB降至-15dB。

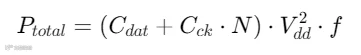

功耗模型与能效突破

-

C:数据路径电容(含互连线路与ESD) -

C:时钟网络电容 -

N:数据率/时钟频率比

-

降低C:通过RDL布局优化(线宽/间距0.13μm)减少寄生电容; -

提升N:采用PAM-4调制(每符号2比特),在相同符号率下数据率翻倍,降低单位比特时钟功耗; -

电压缩放:将Vdd从1.2V降至0.8V,动态功耗降低44%。

多物理场联合仿真方法

技术趋势:光互连与AI驱动优化

总结:协同优化推动算力边界

往期推荐

|

|||

|

|||

|

牛芯半导体(深圳)股份有限公司(简称“牛芯半导体”)成立于2020年,聚焦提供IP授权与定制、IP代理服务、依托IP技术为客户提供芯片整体解决方案及芯片设计服务。

牛芯半导体在主流先进工艺布局SerDes、DDR等高中端接口IP,产品广泛应用于人工智能、消费电子、网络通信、数据存储、汽车电子、医疗电子等领域。

未来,牛芯半导体持续响应IP市场需求,适应不断演进的接口技术和日益拓展的接口互联场景,赋能数智时代下的千行百业。