本文转载自硬件大课堂,转载文章仅供学习和研究使用。

概述

-

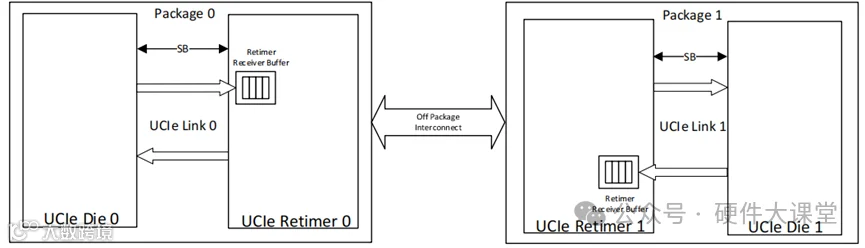

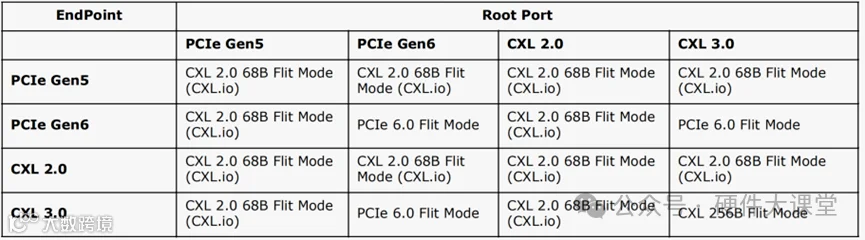

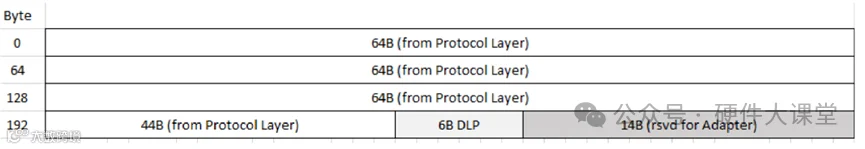

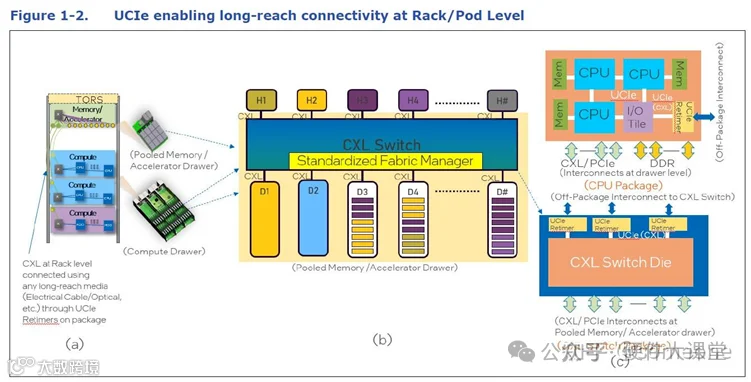

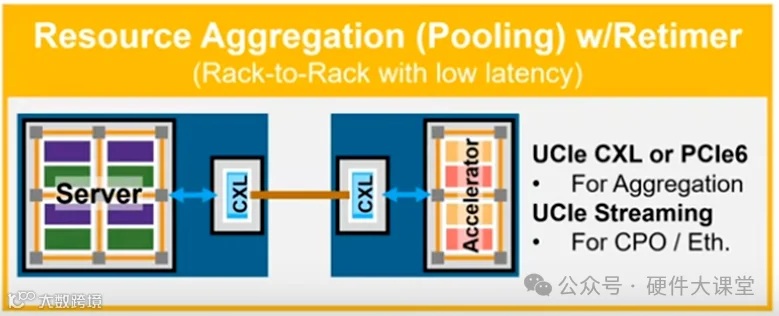

Retimer能够使用当前传输的协议(如PCIe或CXL)底层定义的FEC与CRC进行传输保障,前提是使用的封装外连接能够正确识别当前协议栈下传输中可能出现的错误模型。此时UCIe链路将会被设置为使用原始模式来传输其所使用的协议的bit流。这种情况下,需要在UCIe Die上调整队列大小以满足底层数据往返延迟。 -

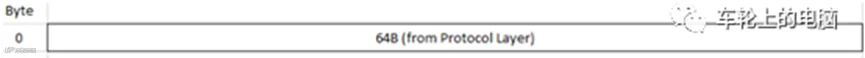

累Retimer允许提供必要的FEC,CRC和重传功能以满足片外互联的误码率要求。在这样的情况下,Flit将会通过三个独立的链路传输。每一个UCIe Retimer对其同一封装下的UCIe Die执行独立的Ack/Nak握手并且与远程Retimer伙伴也执行独立的Ack/Nak握手。 -

Retimer通过使用自定义的FEC替代原有PCIe或CXL定义的FEC,或者在已有PCIe或CXL定义的FEC的基础上增加自定义的FEC,但使用当前底层协议实现的CRC和重传机制。在这种情况下,需要在UCIe Die上调整队列大小以满足底层数据往返延迟。

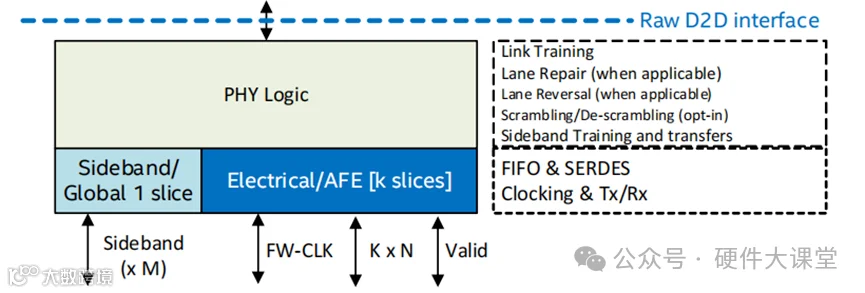

UCIe组件

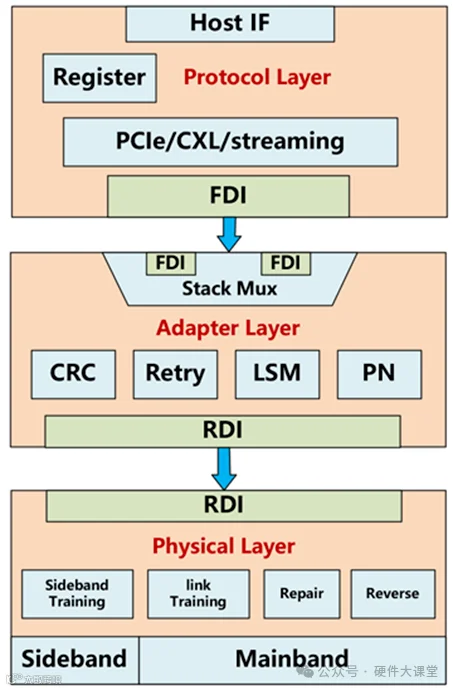

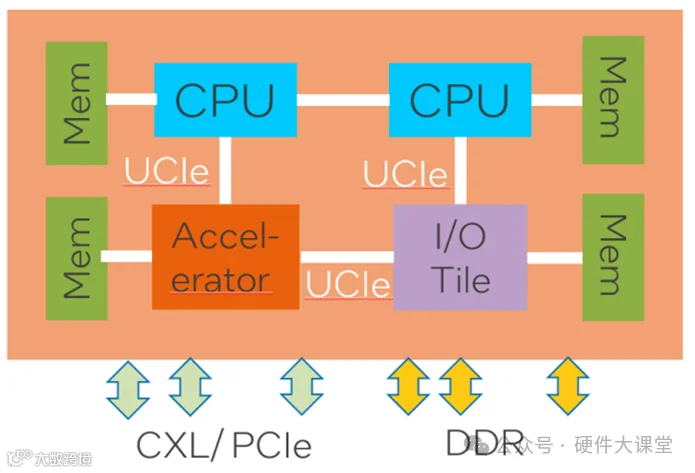

架构设计

软件架构

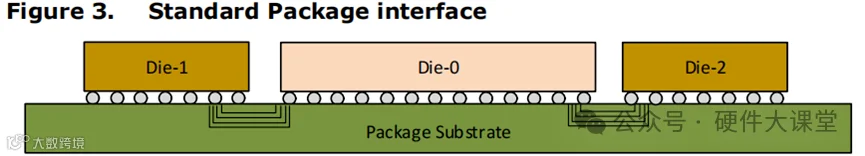

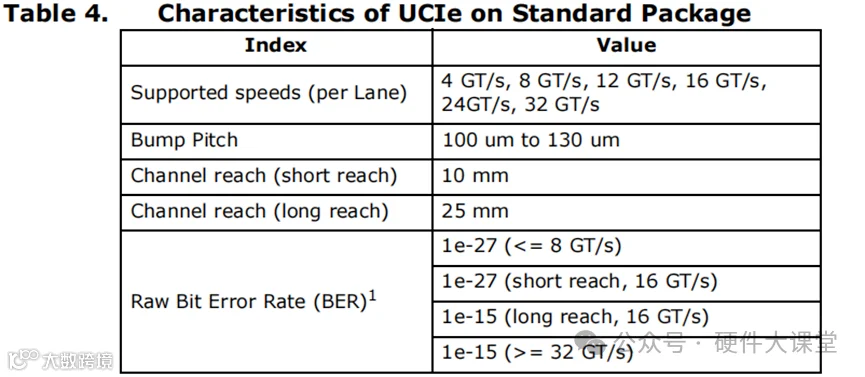

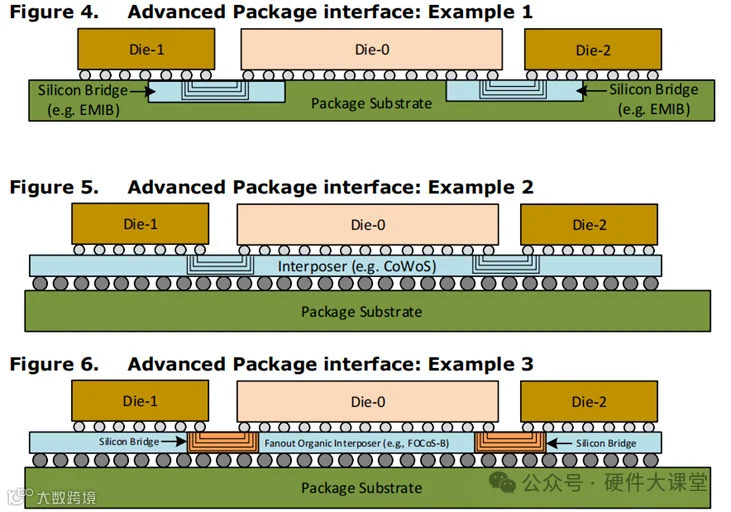

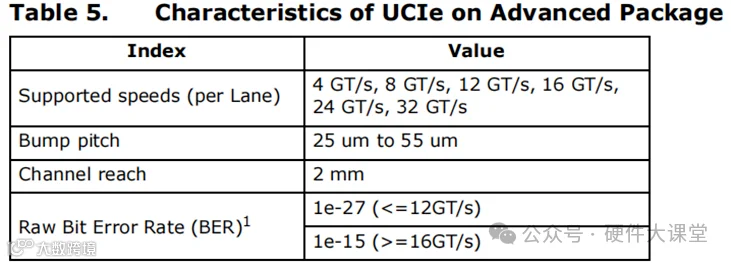

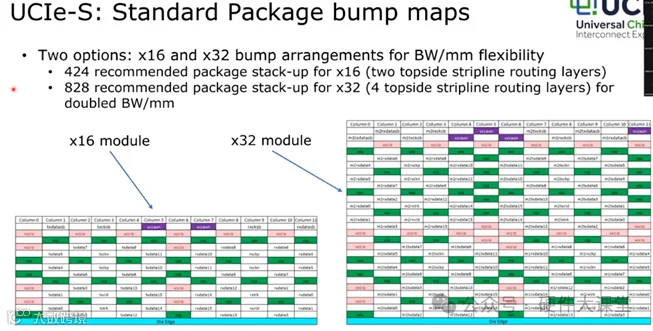

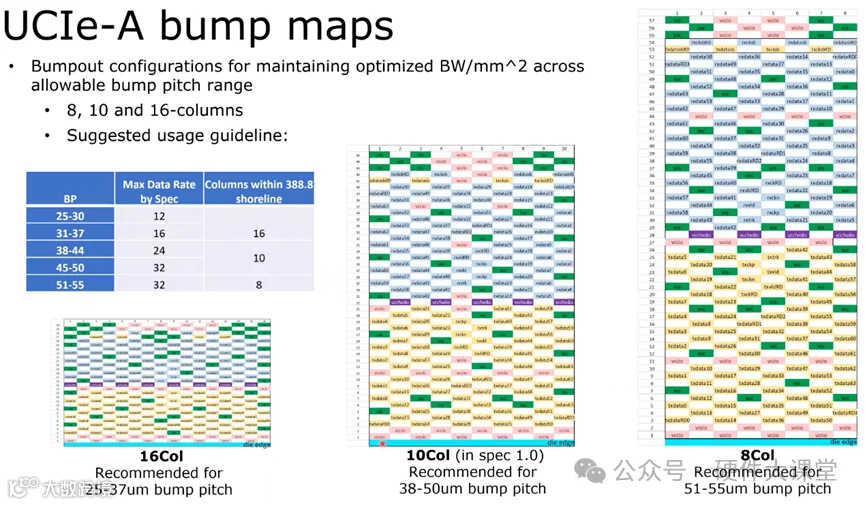

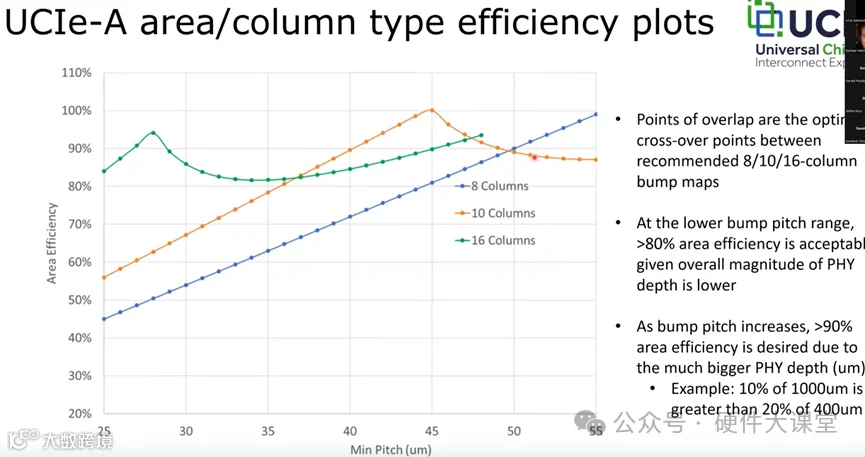

封装

往期推荐

|

|||

|

|||

|

牛芯半导体(深圳)有限公司(简称“牛芯半导体”)成立于2020年,聚焦接口IP的开发和授权,并提供相关整体解决方案,致力成为全球领先的IP供应商。

牛芯半导体在主流先进工艺布局SerDes、DDR等中高端接口IP,产品广泛应用于消费电子、网络通信、数据存储、人工智能、汽车电子、医疗电子等领域。

未来,牛芯半导体持续响应IP市场需求,适应不断演进的接口技术和日益拓展的接口互联场景,赋能数智时代下的千行百业。