本文转载自高速射频百花潭,转载文章仅供学习和研究使用。

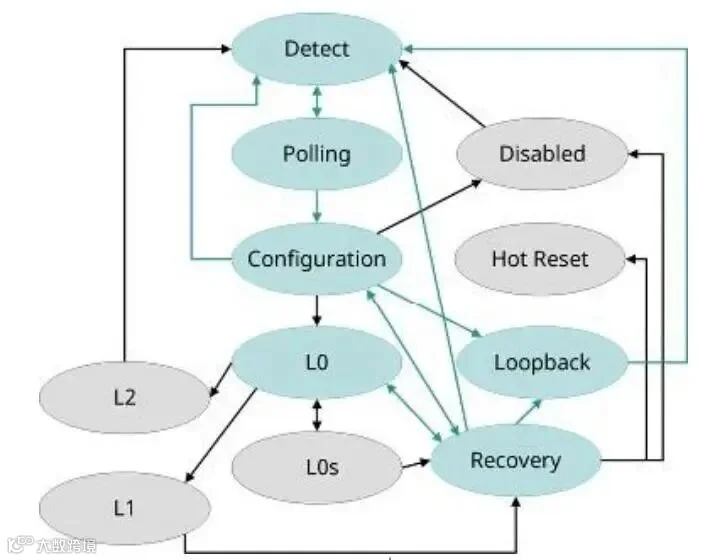

链路训练

-

检测:接收机检测收到的发端信号。上电开始,发端以2.5 GT/s的速度发送PCIe 1.0信号。 -

轮询:接收机同步波形并确定位速率和极性。 -

配置:确定通道宽度,即PCIe信道数。 -

L0:启用链路训练。 -

恢复:发端按照根据预设的FFE tap或者根据上一工作状态优化的一组tap 工作。上电时,它在没有FFE的情况下工作,这等同于将所有tap设为1。PCIe 2.0有两组preset,PCIe 3.0有10组preset,PCIe 4.0和5.0都有 11组preset,依次标为P0、P1、...P10。 -

环回:收端使用内置的系统测试功能,例如CRC,来检查训练序列同步信号的BER性能。 -

a. 如果BER性能是可以接受的,并且系统以低于PCIe 5.0的速率(即32 GT/s)运行,则收端向发端发送请求以提高数据速率,换言之,从PCIe n升级到PCIe n+1,然后,接收器返回到检测阶段。 -

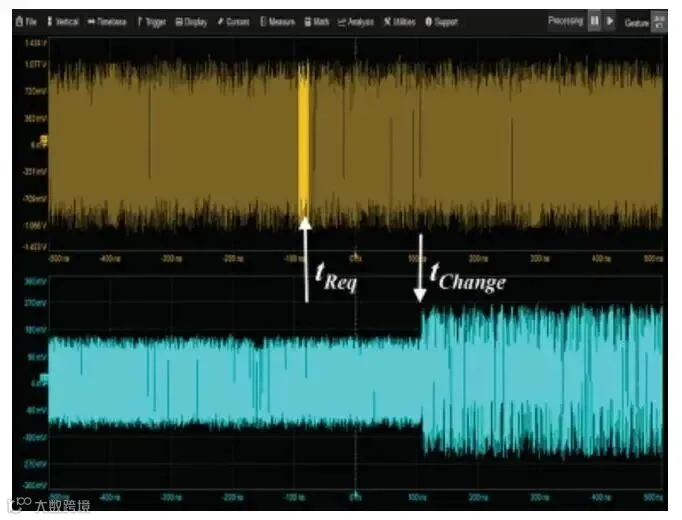

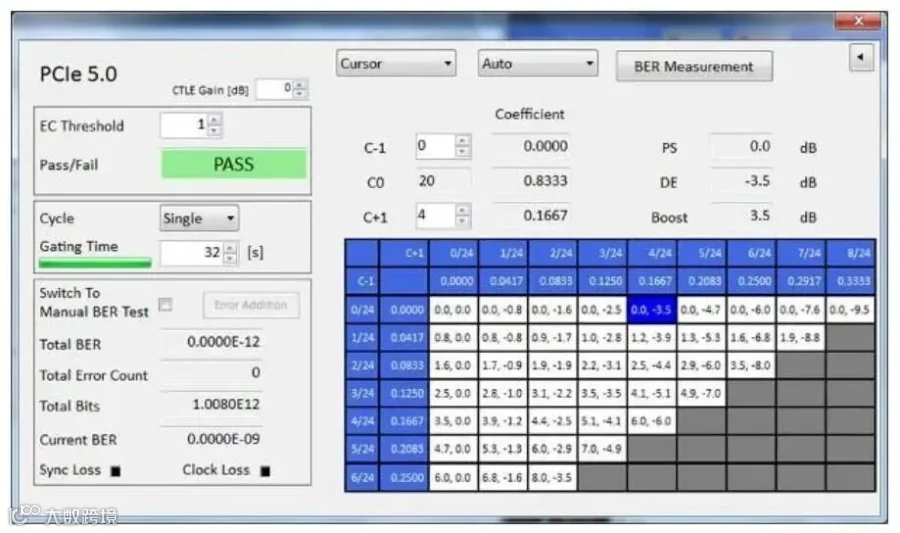

b. 如果BER性能不可接受,但是链路训练时间未超过最大时限,则会发生以下一种或多种情形: i. 收端发送请求,请求发端发送不同的FFE tap:递增、递减、保持不变或加载另一个预设。 ii. 收端修改自己的均衡方案,例如,调整CTLE增益和/或DFE tap,但请注意,PCIe仅指定接收器的BER性能,而不指定均衡技术。然后,系统返回到恢复阶段。 -

c. 如果链路训练时间超过了最大时限,并且接收器尚未找到一种均衡方案以使它能以最大允许BER或更高的BER工作,或者接收器失去同步,则系统将恢复为较低的数据速率。

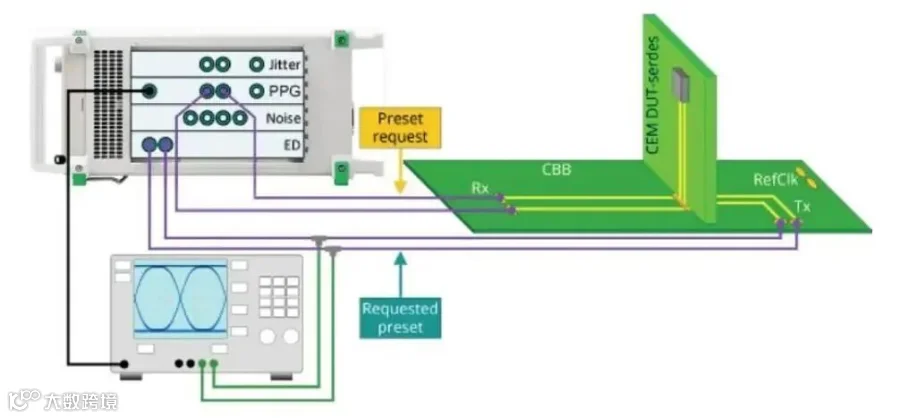

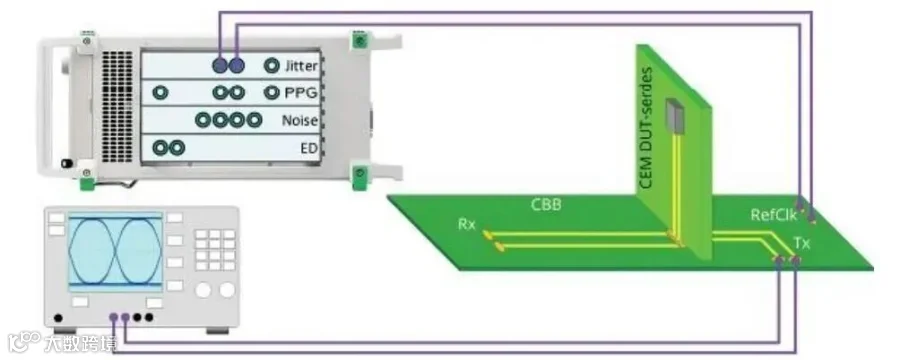

发端链路均衡测试

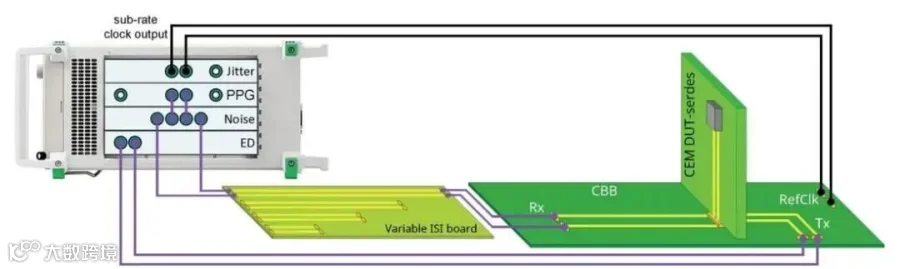

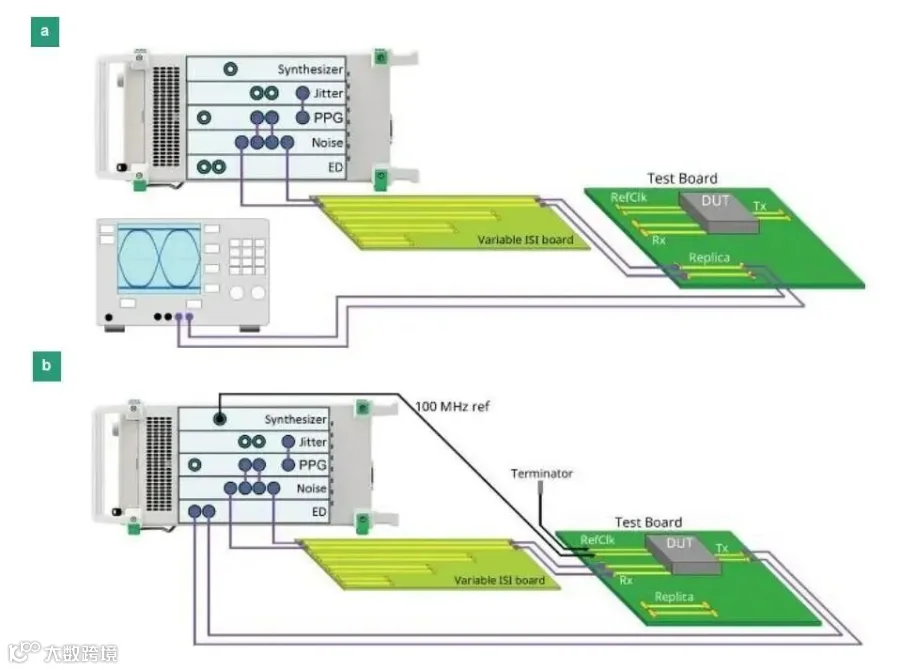

接收机链路均衡测试

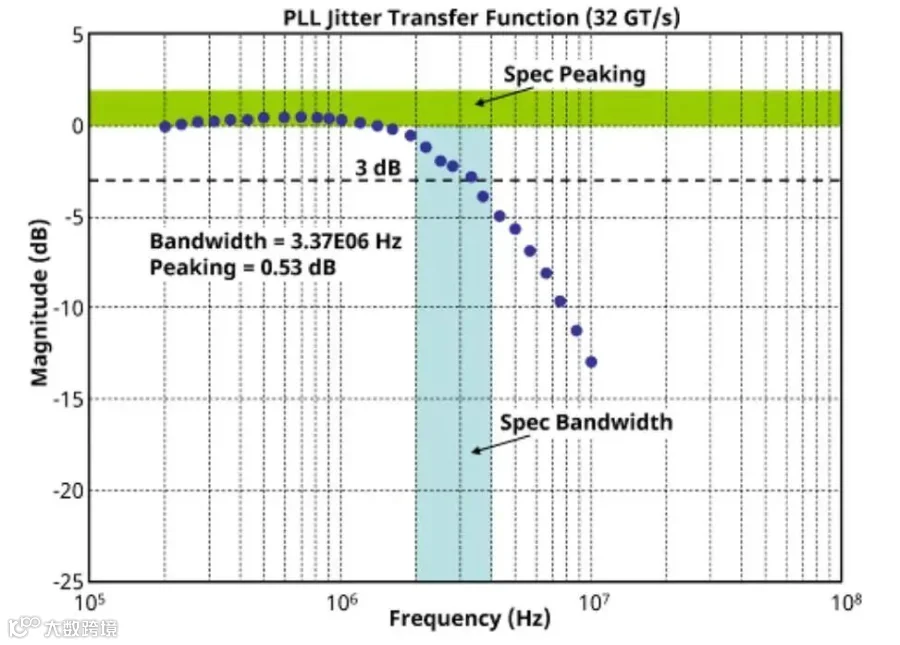

发端PLL带宽测试

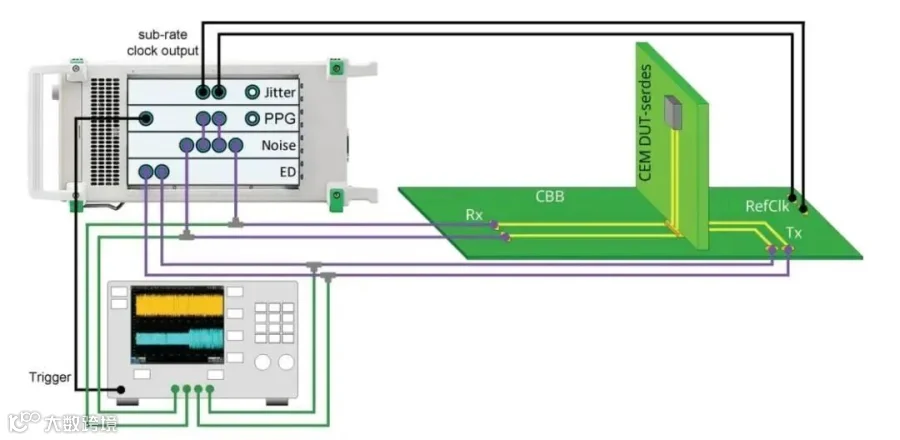

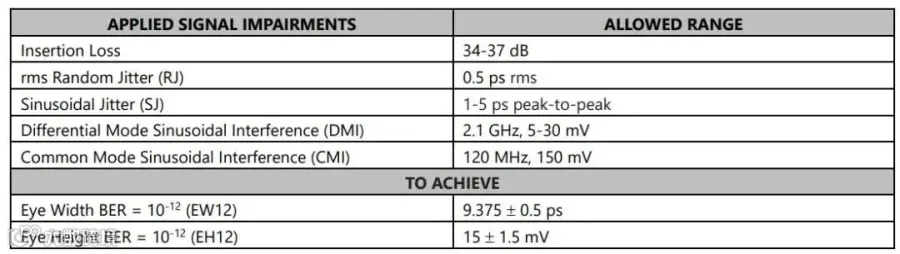

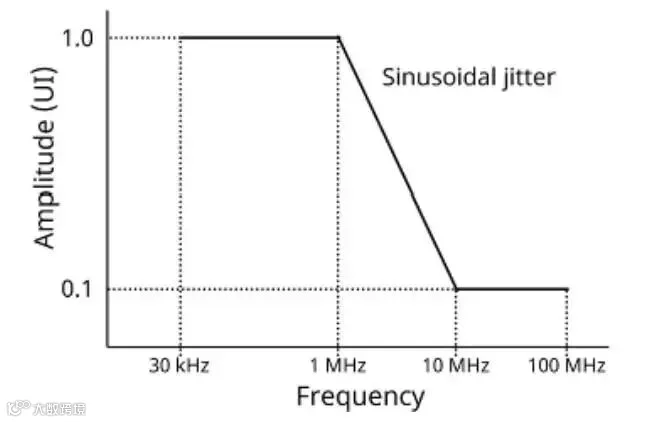

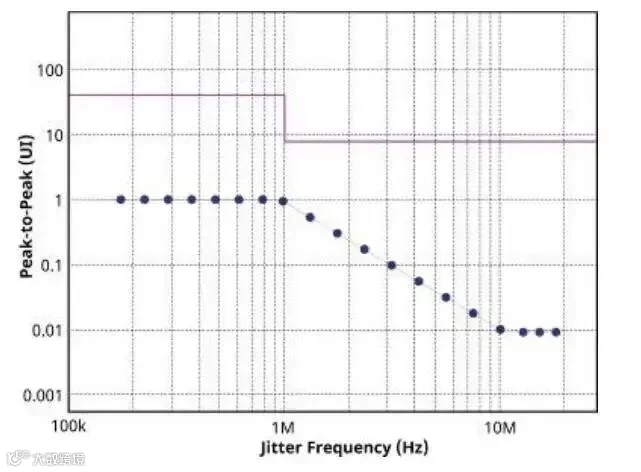

接收机抖动容限测试(JTOL)

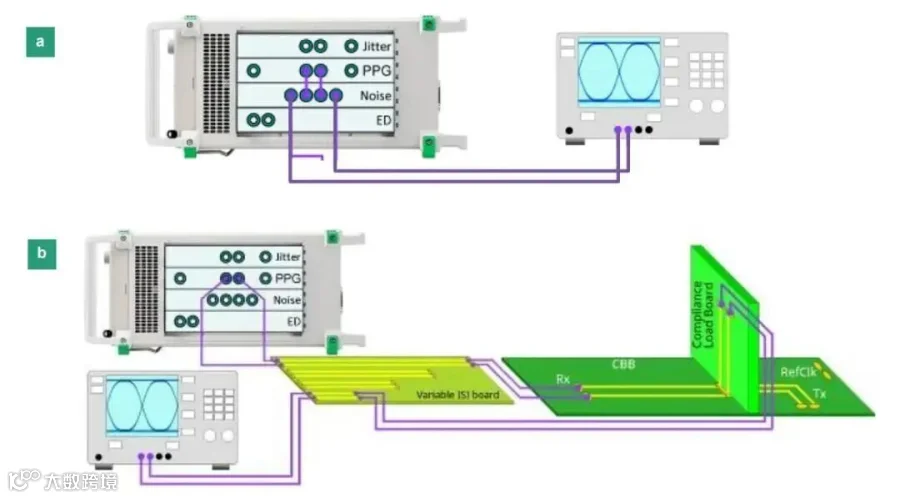

BASE规范符合性测试

往期推荐

|

|||

|

|||

|

牛芯半导体(深圳)股份有限公司,专注于高速互联技术的研发和持续创新,拥有完全自主可控的知识产权,提供全栈式接口IP授权和高速互联芯片的定制方案,赋能芯片国产化;已服务客户超百家,涵盖智能驾驶、人工智能、特种计算、高端半导体设备等领域,致力成为全球领先的高速互联半导体公司。