本文转载自高速射频百花潭,转载文章仅供学习和研究使用。

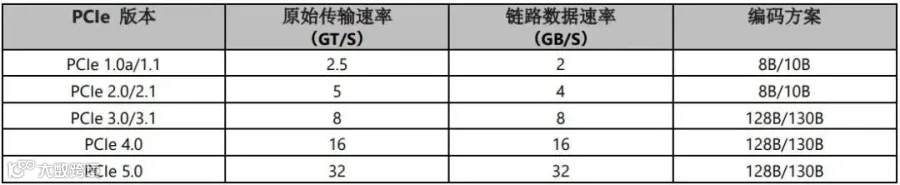

PCIe Gen 5简介

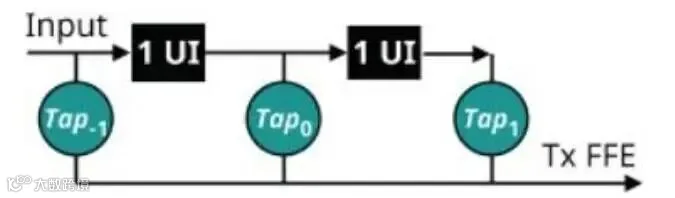

32 GT/s下NRZ的挑战

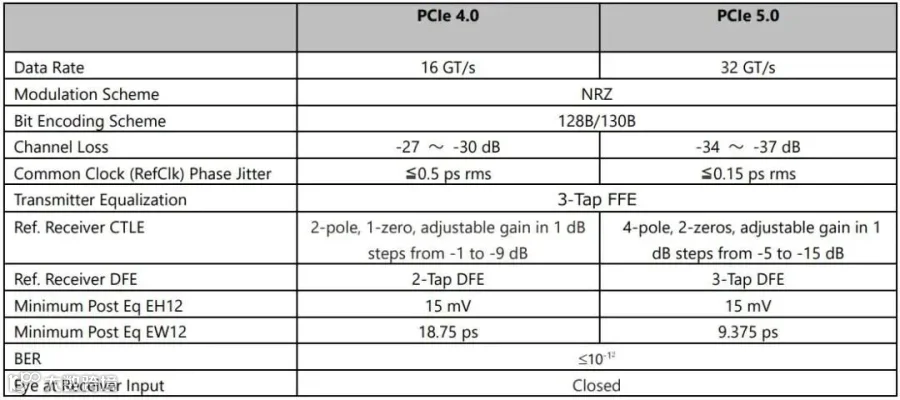

PCIe 4.0和5.0 SerDes要求比较

-

BASE规范定义了芯片级性能,这是一份由上千页内容组成的综合文档。 -

CEM规范规定了插卡连接器的最低性能。 -

测试规范设置了一致性测试的规则。

往期推荐

|

|||

|

|||

|

牛芯半导体(深圳)股份有限公司,专注于高速互联技术的研发和持续创新,拥有完全自主可控的知识产权,提供全栈式接口IP授权和高速互联芯片的定制方案,赋能芯片国产化;已服务客户超百家,涵盖智能驾驶、人工智能、特种计算、高端半导体设备等领域,致力成为全球领先的高速互联半导体公司。