芯片虽能在方寸之间执行数十亿次运算,却极为脆弱,易受物理损伤和环境因素影响,未经封装保护的裸露硅片难以长时间工作。

封装为芯片提供关键保护,确保其可靠供电、数据连接及高效散热。但如今,每一环节的优化都面临严峻挑战。

(来源:Mckinsey)

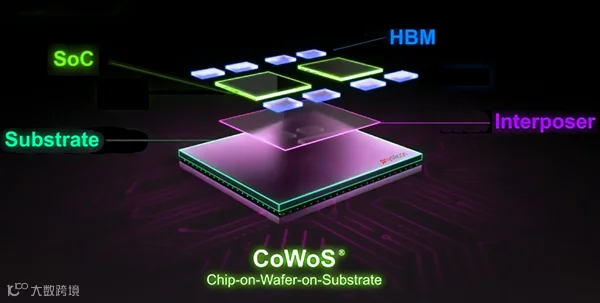

过去几十年,摩尔定律驱动半导体性能持续翻倍,但先进制程研发成本激增且物理极限逼近。行业转而探索先进封装技术,通过多芯片协同设计突破性能瓶颈。例如台积电的CoWoS与HBM堆叠封装,显著提升AI芯片的互连密度与带宽。

图 | CoWoS 先进封装结构示意图。该技术通过硅中介层实现逻辑芯片与高带宽内存的极高密度互连,缩短信号传输距离,提升AI加速器性能。(来源:AnySilicon)

先进封装被视为"接棒摩尔定律"的关键路径。英伟达技术总监Sandeep Razdan指出,当前性能驱动核心已从单芯片算力转向系统整体架构,封装从"收尾工作"升级为性能决定性因素。但先进封装自身正面临重大瓶颈。

先进封装的核心挑战

翘曲问题的成因与影响

今年iMAPS大会上,"翘曲"成为高频关键词。该现象源于封装内部材料热膨胀系数不匹配:当温度超过特定聚合物玻璃化转变点,材料硬度骤降、热膨胀系数剧增,导致封装形变。翘曲会连锁引发芯片贴合偏差、键合良率下降及成本飙升。尤其AI芯片封装尺寸逼近光罩极限时,微小弯曲即可触发系统性良率危机。

三大解决方案路径

行业主要从三方面应对挑战:

材料层面,尝试以玻璃基板替代传统有机塑料。玻璃平整度高、热膨胀系数与硅片接近,可显著抑制翘曲。但其脆性易引发微裂纹和搬运损伤,大尺寸下残余应力累积问题同样突出。

互连技术层面,混合键合技术直接熔合芯片表面铜层,实现最高互连密度,对AI芯片至关重要。然而,键合间距缩至2-3微米以下时,铜层高密度导致应力撕裂风险,且对纳米级污染极度敏感,良率控制难度剧增。

空间架构层面,背面供电将电源网络转移至硅片背面,释放正面数据信号空间。但硅片需研磨至5微米极限厚度,对临时键合材料精度提出严苛要求,稍有偏差即影响HBM等堆叠存储芯片良率。

这些工艺步骤相互牵制,每一步引入的应力和误差均会蚕食后续工艺窗口。工程师必须精准控制应力传递,避免系统性失效。

全球竞争与中国厂商的机遇

先进封装已进入"代工2.0"时代,台积电计划2026年将CoWoS月产能提升至15万片晶圆当量,头部企业主导技术演进。长电科技、通富微电等中国大陆厂商虽加速产能爬坡,但在2.5D/3D高端市场份额仍有限,直面材料交互数据与热历史模型构建的护城河。

技术热潮呈现市场分层:超大尺寸封装由AI与高性能计算驱动,而汽车电子等领域仍依赖成熟方案。国内封测企业需针对不同市场采取差异化策略,避免盲目追逐前沿概念。

无论是技术引领者还是追赶者,最终考验在于将复杂材料、结构与热历史的系统性挑战转化为稳定良率。留给企业摸索工艺窗口的时间正在快速收窄。