谈及芯片制程要从晶体管说起,晶体管是组成芯片的基本单位,一颗芯片内含的晶体管数量多到百亿,少则十几或者几百。如果说芯片是房子,那么晶体管就是组成房子的砖块。

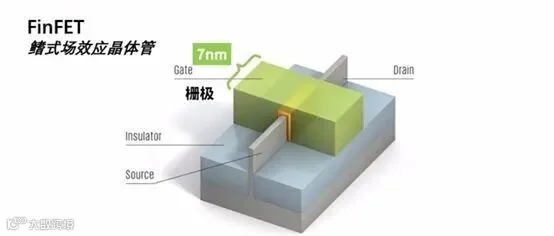

大家在“缺芯危机”、“中美贸易战”的相关新闻中,经常会听到被用来度量芯片制造发展水平的长度单位,诸如7nm、5nm、3nm等等。这些数字代表芯片的大小吗?其实不是,其具体是指芯片晶体管栅极宽度的大小。

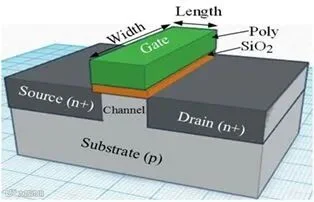

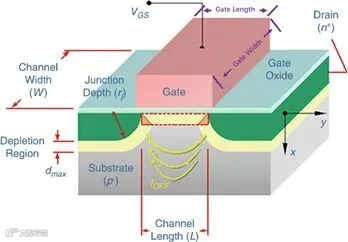

晶体管是由源极Source、漏极Drain和位于二者之间的栅极Gate组成。最开始,平面制程工艺尺寸是指源极到漏极的空间距离,即沟道长度。但是现在的沟道长度并不好测量,它会根据掺杂扩散,大小尺寸不一,而栅极长度近似沟道长度,且栅极长度观察测量更为直观,因此采用栅极长度作为制程工艺参考标准。

晶体管基本结构

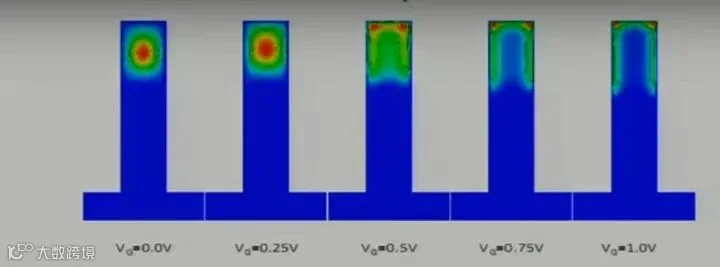

栅极是晶体管的控制端。栅极和源极之间的的电压差,控制了漏极和源极之间的电流大小。你可以把栅极当作开关,当Vgs为高时导通,电流从源极流入漏极,栅极就相当于水龙头的开关。而栅极的最小宽度(栅长),就是芯片制程工艺中的数值。栅极的宽度则决定了电流通过时的损耗,表现出来就是手机常见的发热和功耗,宽度越窄,功耗越低。可以这么理解如果打开水龙头的力越小就相当于制程越小。

对于芯片制造商而言,主要就要不断升级技术,力求栅极宽度越窄越好。不过当宽度逼近20nm时,电场干扰变多,栅端可能“关不严”,对电流控制能力急剧下降,会出现“电流泄露”问题,即所谓的短沟道效应。一方面,电流泄露将直接增加芯片的功耗,为晶体管带来额外的发热量,影响使用寿命;另一方面,电流泄露导致电路错误,信号模糊。为了解决信号模糊问题,芯片又不得不提高核心电压,功耗增加,陷入死循环。因而,漏电率如果不能降低,CPU整体性能和功耗控制将十分不理想。

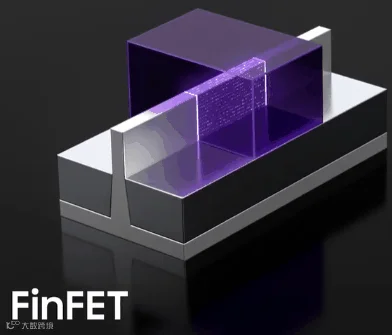

直到1999年,胡正明教授发明了鳍式场效应晶体管FinFET,加强了栅极对沟道的控制能力,从而减小短沟道效应。由此才在一定程度上延缓了该问题,如今台积电、三星能做到的5nm/7nm都依赖此项技术。

FinFET晶体管

FinFET的工作原理

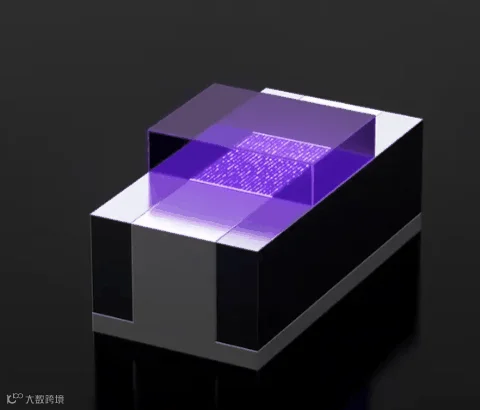

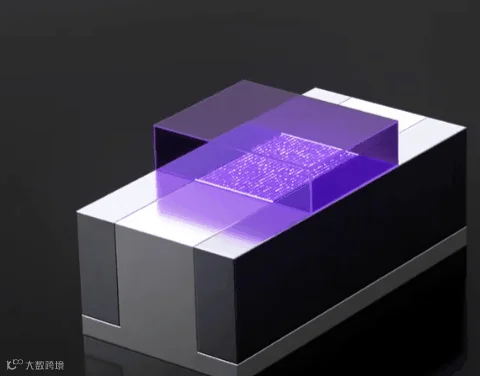

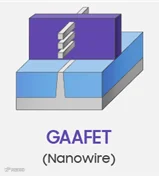

但是到了3nm阶段,FinFET的三面栅的控制作用减弱,短沟道效应再次凸显。直到下一世代的晶体管结构即所谓Gate-All-Around环绕式栅极技术(简称为GAA结构)出现,问题才得以缓解。它可以简单理解为沟道被栅极四面包裹,从而降低操作电压、减少漏电,降低芯片运算功耗与操作温度,从而继续为摩尔定律续命。

GAA晶体管

无论是FinFET还是GAA结构,都是人类不断研发新的工艺手段来逼近理论极限,实现难度非常大,适用范围也有局限性。在更广阔的领域里,如工业以及军事领域,先进制程芯片反而没有成熟制程芯片可靠,它们更关注的是芯片在各类极端环境下的可靠性和耐久度。因此,对于一个复杂而庞大的芯片产业来说,制程并不是衡量芯片价值的唯一标准。

沃泰芯半导体

用芯改变中国,

让世界选择中国芯

沃泰芯专业从事第三代半导体的研发、设计和制造。