功率MOSFET的设计

1、纵向结构设计

1.1 n-漂移区的设计

n-漂移区直接关系到击穿电压和导通电阻,设计时应根据器件的特性参数要求进行折中考虑,在满足击穿电压的前提下,使n-漂移区宽度Wn-与外加电压下n-漂移区耗尽层的展宽 WD相等,此时导通电阻Ron最小。此外,n-漂移区采用非均匀外延掺杂来代替均匀掺杂,有利于降低Ron。n-漂移区的非均匀外延掺杂浓度分布和厚度可分别用下式来表示:

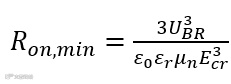

与上式对应的最小电阻为:

比均匀掺杂时的低12.5%。

1.2 P体区的设计

p体区的设计主要考虑击穿特性与开通特性。

p体区次表面浓度NPJ与沟道掺杂浓度有关,决定了阈值电压的高低。NPJ越高,则阈值电压越高。p体区厚度Wp由n+源区和p体区的结深决定,并与沟道长度L有关。沟道长度L通常为0.8Wp。Wp越厚,即L越长,会导致跨导减小、沟道电阻Rch增大。所以,沟道长度与沟道掺杂浓度的设计需同时考虑阈值电压、沟道电阻及击穿电压。当功率MOSFET的 UT为3~5V时,NPJ在(3~5)×1017 cm-3范围内;当沟道长度L为1~2μm时,p体区厚度 Wp约为1.25~2.5μm。

1.3 P阱区的设计

为了防止VDMOS结构中寄生的npn晶体管工作,需减小p 体区的横向电阻RB。p体区的浓度Np越高,厚度Wp越厚,RB越小,但Wp受L的限制。为了避免Wp对L的影响,通常在p体区制作之前,先通过硼离子(B+)注入在其下方形成一个p+阱区, 如图1所示,以增加p体区的掺杂浓度和厚度,从而有效地降低p体区的横向电阻RB,提高VDMOS的可靠性。

图1 VDMOS剖面及横向掺杂浓度分布

2、横向结构设计

2.1 元胞图形的设计

图2 VDMOS电流分布及元胞图形

图3 各种元胞图形的品质因子随a/s的变化趋势

功率MOSFET的电流与沟道宽度成正比,为了提高电流容量,通常在有限的芯片面积上将多个元胞并联起来,以增大沟道宽度。图2给出了圆阱六角元胞的VDMOS电流分布及其对应的元胞图形。其中a表示p体区尺寸,s表示p体区间距,b表示元胞间距(Cell Pitch),为元胞重复单元。若用 Acell表示元胞总面积,A′表示元胞边角结合处不能流过电流的无效区面积,通常将A′/Acell定义为芯片牺牲率。A′/Acell值越小,则Ron越小。Ach表示垂直导电沟道的有效面积,通常将Ach/Acell称为品质因子。

在元胞图形的设计中,若Ach/Acell值越大,则Ron越小,故Ach/Acell值决定了芯片面积一定时Ron的大小。图3给出了不同元胞图形的品质因子随元胞参数a/s的变化曲线。当p 体区间距s与p体区尺寸a相等时,即s/a=1时,方形或六角形元胞图形的品质因子最大, 而三角形与条形的品质因子较小。计算表明,六角形及方形元胞的牺牲率最小,圆形元胞的牺牲率最大。相比较而言,由于三角形元胞的电场容易集中,会导致漏源击穿电压降低,无实用价值;圆形元胞因牺牲率大而很少用;六角形与方形的Ach/Acell值和A′/Acell值基本相同,并且六角形元胞能够紧密结合,电流分布均匀,芯片利用率高。所以,低压器件多采用六角形元胞结构,高压器件对元胞结构的几何形状并无特别要求,通常采用易于制版及光刻的方形元胞。

2.2 元胞密度设计

对低压功率MOSFET而言,元胞密度对降低沟道电阻很关键。这是由于低压器件的外延层厚度较薄,VDMOS中各元胞的电流路径基本上不发生交叠(见图4a)或者部分交叠(见图4b),此时减小线宽或增加沟道宽度,可以提高元胞密度,有利于降低导通电阻。对中、高压功率MOSFET而言,由于沟道电阻对导通电阻的贡献很小,所以元胞密度不是很重要。因为随着漏源击穿电压增加,外延层厚度不断增加。如图4c所示,当外延层厚度较厚时,各元胞的电流路径几乎完全发生互相交叠,此时整个芯片可视为一个整块导体,与芯片元胞数基本无关,此时提高元胞密度对降低导通电阻没有作用。反而,由于漂移区电阻RD与通流截面积成反比,p体区间距越大,越有利于减小RD,从而减小导通电阻Ron。所以,为了减低高压器件的导通电阻,并避免JFET的影响,p体区间距尽可能大些,但应小于p体区最大元胞间距smax。否则,每个元胞像一个单独的pn结,其边、角电场强度很高,导致击穿电压降低。

图4 外延层厚度对电流分布的影响

2.3 有效面积和元胞数的确定

功率MOSFET的导通电阻等于特征导通电阻与有效面积之比。当导通电阻的指标给定后,可根据特征导通电阻和导通电阻值之间关系计算有效面积。元胞数可根据电流容量来计算,电流容量与元胞数之间的关系为I=J·A·n。这里,I为导通电流;J为电流密度;A为元胞中有效导电区的面积;n为元胞数。如已知I=10A、J =70A/cm2、A=138.43μm2,所以很容易求出元胞个数为1.032×105。通常每个元胞的电流容量为0.6~0.9mA,那么2A器件一般需设计成3600个元胞,而对于5A/600V器件则需设计成9000~11000个元胞。

2.4 栅极结构的设计

栅极特性要求接触电阻低、击穿电压高、漏电流及输入电容小。栅电极材料可采用金属铝和重掺杂多晶硅。实际工艺中,利用磷离子注入同时对多晶硅栅和n+源区进行掺杂。为了降低栅极分布电阻的影响,在版图布局时,通常将栅极压焊点处的金属引伸到离压焊点较远的元胞处,且引伸的金属条与其下面多晶硅相接触,如图5所示。图中的虚线箭头表示栅极信号流的方向与路径,金属栅极采用了延伸结构,被源区包围。芯片外围采用场限环结终端。

图5 VDMOS的版图布局