今天我们EGO1动手练习部分要做的是一个数字钟实验。这个实验在参考教材《基于Xilinx Vivado的数字逻辑实验教程》的第3章第1节,是FPGA设计实验部分的简易数字钟实验。

该实验使用EGO1板卡上的四位数码管,实现计分和秒的功能。要实现秒计数,需要设计一个六十进制秒计数器;要实现分计数,需要设计一个六十进制分计数器。能够实现计数功能的数字芯片很多,本实验选取74LS90为核心元器件。

我们通过在原理图设计界面搭建电路的方式来完成这个数字钟电路搭建。然后可以通过编写Testbench文件Digital_Clock_tb.v来给这个数字钟电路施加测试激励信号,并进行仿真。

数字钟电路的仿真激励如下所示:

1 module Digital_Clock_tb( );

2 reg GND;

3 wire [6:0]a_to_g;

4 wire [3:0]an;

5 reg clk;

6 reg clr;

7 wire dp;

8 parameter PERIOD=10;

9 design_1_wrapper dut

10 (

11 .GND(GND),

12 .a_to_g(a_to_g),

13 .an(an),

14 .clk(clk),

15 .clr(clr),

16 .dp(dp)

17 );

18 initial

19 begin

20 clk = 0;

21 GND=0;

22 forever

23 begin

24 #(PERIOD/2) clk = 1;

25 #(PERIOD/2) clk = 0;

26 end

27 end

28 initial

29 begin

30 clr = 0;

31 #10 clr = 1;

32 end

endmodule

关于实验原理部分的详细讲解,有兴趣的小伙伴们可以查阅参考书的对应章节。

实验源文件准备妥当之后,我们就可以开始动手实践啦。

首先当然是打开Vivado工具咯,这里我们使用最新的2017版本的Vivado开发环境。什么?你还没有安装Vivado么?表担心啦,我们提供有详细的Vivado安装流程,请点击这里查看。

Vivado开发环境成功打开后,它的主界面如下。

接下来就让我们开始使用Vivado完成这个实验吧。如果有对Vivado操作不熟悉的小伙伴们也不用担心啦,我们提供有STEP-BY-STEP的指导噢。请点击这里查看详细的Vivado实验操作流程。

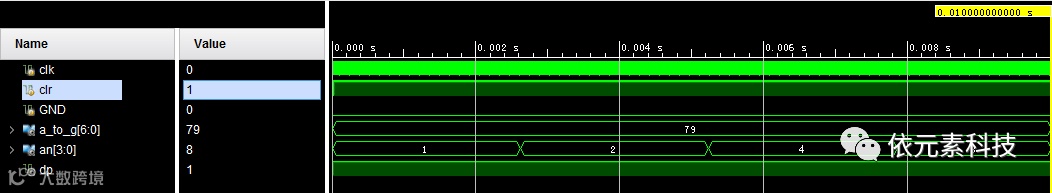

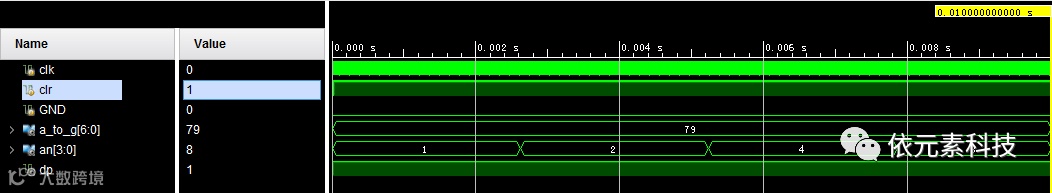

首先,我们进行实验仿真。下面是仿真的结果。

同时,我们可以在Vivado中查看我们RTL所对应的原理图。

在完成Vivado FPGA综合流程后,我们还可以看到这段电路综合后的原理图。

最后,我们完成设计的整体实现,可以看到这段电路在实际的FPGA芯片中的线路图。

接下来,就可以在硬件平台上下载验证啦。当然,我们也有使用EGO1口袋实验平台来进行硬件下载的详细步骤介绍哟,请点击"阅读原文"查看。

硬件配置完成后,我们就可以在EGO1平台上来验证我们的设计啦,这个设计中我们将EGO1开发板的SW0和SW1分别作为clr和GND的输入,数码管作为输出。将SW0拉高后,可以看到4位数码管点亮,并开始计时,低两位代表秒,高两位代表分。好啦,各位小伙伴们大家看看我们的电路计算正确么?