文章来源:恒元光电

文章来源:恒元光电

一代材料,一代器件,一代产业,一个时代。铌酸锂晶体是一种集压电、电光、声光、光弹、非线性、光折变及激光活性等效应于一身的罕见晶体,加上自身机械性能稳定、易加工、耐高温、抗腐蚀、原材料来源丰富、价格低廉、易生长成大晶体的优点,尤其是实施不同掺杂后能呈现出各种各样的特殊性能,是至今人们所发现的光子学性能最多、综合指标最好的晶体,具有十分广阔的市场应用前景,因此也被人称为光子时代的“光学硅”材料,被广泛的应用于高性能滤波器、电光器件、全息存储、3D 全息显示、非线性光学器件、光量子通信等方面。

《激光与光电子学进展》于2024年第11期(6月)推出创刊六十周年系列专题之“铌酸锂光子学器件”。此系列专题集中展示了我国在铌酸锂光学器件领域的最新研究进展,有助于促进学术交流,推动铌酸锂相关领域向纵深发展。我们本次将对专题中的“铌酸锂集成光子芯片端面耦合器件”一文进行分享,让大家更好地了解铌酸锂及其相关应用。

“铌酸锂集成光子芯片端面耦合器件”是由南开大学泰达应用物理研究院薄方教授及其团队受邀发表的文章。

薄膜铌酸锂(TFLN)具有优异的电光和光学非线性特性,是开展电光调制器、非线性光学频率转换器等相关研究的重要平台。然而,由于 TFLN 片上光波导与光纤模场尺寸存在显著差异,严重限制了二者之间的高效耦合。因此,高效率端面耦合器成为了突破 TFLN 集成光学芯片应用限制瓶颈的重要手段。该文章将对 TFLN 端面耦合器的研究进展进行系统综述,首先介绍常见的几种参与端面耦合的光纤特性;然后,介绍端面耦合器中铌酸锂端面耦合波导的典型结构;最后,对端面耦合器研究现状、存在的问题等做出总结,并展望未来可能的发展方向。

集成光子学为光通信、传感、光计算、生物医学、量子信息处理等领域提供了低成本、高集成度、可扩展的解决方案。硅、氮化硅、碳化硅、氮化铝等材料平台均可用于制备集成光子学器件。然而,到目前为止,基于单一的材料平台还无法完全满足集成光子学对光源、光控制、光探测等的多种光学元器件的需求。铌酸锂晶体因具有较宽的透明窗口,优秀的电光、声光和非线性光学等特性,被誉为“光学硅”,是集成光学平台制备材料的有力候选者。

基于体材料铌酸锂的集成光学器件研究已经取得了许多重要的进展。基于体材料的钛扩散、质子交换工艺实现的波导等光学元器件,其折射率对比度低,波导模式面积大(一般模斑直径为 5~10μm),集成度受限。而基于智能切片(Smart cut)工艺实现的薄膜铌酸锂(TFLN)厚度一般为几百纳米,结合紫外光刻、电子束曝光、离子束刻蚀等半导体微加工工艺,可以实现微米/亚微米尺度的光波导制备,芯片集成度大幅提升,因此TFLN被认为是开展集成光子学研究的理想平台之一。

TFLN光波导宽度通常为1~2μm,厚度通常为500~700nm,而普通单模光纤的纤芯直径通常约8μm,在1550nm波长附近的模场直径接近10μm,二者之间巨大的模场面积差距导致端面耦合的损耗增加。从器件整体性能层面来说,通常TFLN器件的插入损耗为4.5~10.0dB,而光纤耦合损耗在没有端面耦合设计的器件中通常为6~7dB/facet,仍有大幅的优化空间。因此,高效率片上-片外耦合器对能否发挥TFLN片上光学元件的性能起着至关重要的作用,可以大幅提升泵浦光能量利用率和信号光提取效率。

在TFLN集成平台上,光栅耦合和端面耦合是两种实现波导与光纤能量交换的主要耦合方式,如图1所示。其中,端面耦合是一种面内耦合方法,具有耦合带宽大、无偏振选择性等优点。通过设计模斑转换器,将微纳波导中的模场面积扩大,从而与单模光纤、透镜光纤、微透镜等光学器件的模场匹配,来实现高效率耦合。由于端面耦合对器件端面的质量有较高的要求,需要对光纤和波导端面进行切割和抛光等精细处理,以减少光波的反射和散射。在耦合封装过程中,还需要精细控制波导与光纤之间的距离,以防止二者硬接触造成光纤或者样品边缘的损坏。因此,该文将对TFLN端面耦合器的发展现状进行综述,针对技术路线、性能指标等方面进行讨论,同时对相关研究的进一步发展进行展望。

图1 光栅耦合器和端面耦合器示意图

图2从材料、结构、制备工艺和性能等方面,给出了近年来TFLN端面耦合器的发展过程。之后将对相关工作从结构及制备工艺等角度进行详细介绍,主要分为四个部分:倒锥形端面耦合器、悬臂弱波导端面耦合器、异质集成模斑转换器与端面耦合器,以及楔形波导端面耦合器。

图 2 TFLN 端面耦合器的发展

倒锥形结构端面耦合器

2019年,澳洲墨尔本大学Peruzzo课题组报道了单层倒锥形TFLN端面耦合器设计,结构如图3(a)所示。该端面耦合器实现了与锥透镜光纤(MFD~2. 5μm)良好的模场匹配,单端耦合损耗从没有端面耦合器设计时的8.5dB降至2.5dB。

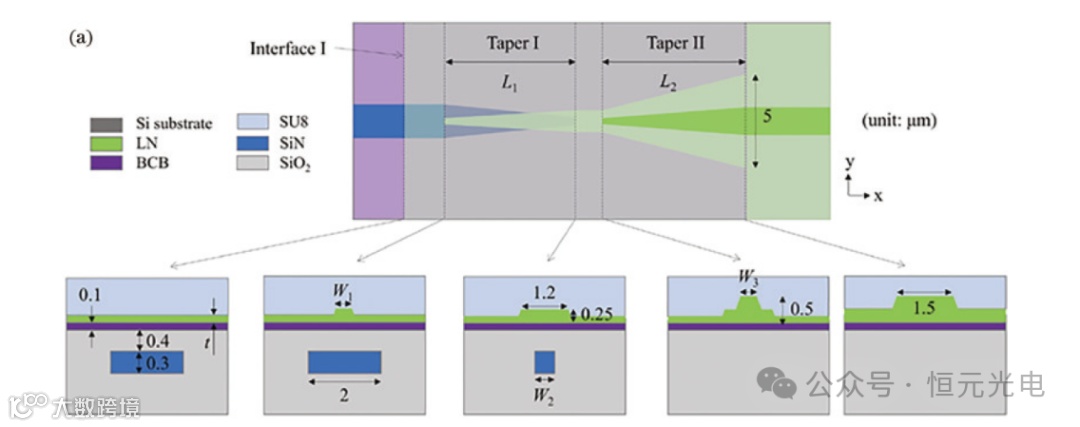

图 3 单层或双层倒锥形铌酸锂波导与包层弱波导端面耦合器结构示意图。(a)单层倒锥形铌酸锂波导;(b)双层倒锥形铌酸锂波导;(c)单层倒锥形铌酸锂波导与氮氧化硅弱波导;(d)双层倒锥形铌酸锂波导与氮氧化硅弱波导;(e)双层倒锥形铌酸锂波导与SU-8弱波导

2019年,美国哈佛大学Marko Lončar课题组,通过电子束曝光(EBL)和套刻工艺,制备了双层倒锥形端面耦合器,结构示意图如图3(b)所示。在该结构中,光纤的模式首先耦合至末端宽度为340nm 的铌酸锂倒锥形带波导中,然后再通过末端宽度为30nm的倒锥形结构耦合到铌酸锂脊波导中,最终实现从光纤到宽度为800nm的铌酸锂脊波导的高效耦合。

北京工业大学王智勇课题组,在铌酸锂脊波导上层引入了氮氧化硅(SiON)弱波导。由于氮氧化硅折射率介于SiO2与铌酸锂之间,使其作为媒介层,不仅可以有效地实现光纤-波导之间的折射率匹配,还可以实现对铌酸锂脊波导模式的扩束,避免波导末端出现过长的窄波导区域,如图3(c)所示。

2021年,华中科技大学夏金松课题组将氮氧化硅带波导与铌酸锂双层倒锥结构相结合,如图3(d)所示,实现了UHNA7与铌酸锂波导之间在横电模(TE)、横磁模(TM)模式下超低耦合损耗分别为0.54dB/facet和0.59dB/facet。中山大学蔡鑫伦课题组展示了使用聚合物材料SU-8波导覆盖在双层倒锥铌酸锂波导结构上的端面耦合器设计,如图3(e)所示,耦合损耗低至0.5dB/facet。虽然聚合物波导提供了成本效益并具有加工灵活性等优势,但在集成光子芯片中的应用,还需要根据特定应用场景及需求权衡性能、成本的利弊。

悬臂弱波导端面耦合器

中山大学蔡鑫伦课题组设计的三层倒锥形结构端面耦合器,结构如下图所示。该耦合器由三层不同末端宽度的倒锥形铌酸锂波导和包覆在铌酸锂波导外的SiO2弱波导构成。通过PECVD工艺形成SiO2覆盖层后,通过氟化氙(XeF2)或六氟化硫(SF6)对Si衬底进行各向同性的干法刻蚀,使下层热氧化层SiO2悬空,与上层通过PECVD 工艺形成的SiO2包层共同形成带波导,而铌酸锂三层倒锥波导被SiO2带波导包裹在中间,当光从光纤耦合进SiO2弱波导后,会通过锥波导逐渐束缚至铌酸锂脊波导中。该设计实现了1550nm与775nm双波段的高效耦合,耦合损耗分别低至1dB/facet和3dB/facet。

图4 三层倒锥形铌酸锂波导与悬臂SiO2弱波导端面耦合器结构

此外,浙江大学刘柳课题组采用了类似的方法,将SiO2波导与Si衬底隔离开,形成悬臂弱波导结构的端面耦合器,并通过引入偏振转换器,成功实现了损耗仅为1.06dB/facet 的偏振复用型端面耦合器。

异质集成模斑转换器与端面耦合器

氮化硅(Si3N4)作为一种与互补金属氧化物半导体(CMOS)技术兼容的材料,其光学折射率约为1.8~2.0,可通过化学气相沉积(CVD)工艺、光刻和离子束刻蚀等工艺制备成薄膜光波导,刻蚀工艺成熟。将Si3N4与铌酸锂进行异质集成,对于提升端面耦合器的性能同样具有可行性。

2023年,浙江大学刘柳课题组采用晶圆键合技术,实现了铌酸锂与Si3N4的高效异质集成。首先,通过PECVD工艺在Si衬底上沉积了4μm厚的 SiO2作为隔离层。接着,通过低压化学气相沉积(LPCVD)工艺在此隔离层上进一步沉积了300nm厚的Si3N4层。随后,通过反应离子束刻蚀技术,形成Si3N4光栅、波导等结构。在制备Si3N4波导后,又在Si3N4 层上覆盖了400nm厚的SiO2包层,并通过化学机械抛光(CMP)处理,以确保顶层SiO2的表面平整性。耦合结构如下图所示,模斑转换损耗仅为0.4dB。

图 5 Si3N4和铌酸锂异质集成模式转换器与端面耦合器

同年,中国科学院半导体所李智勇课题组,在硅基TFLN晶圆上直接通过PECVD工艺沉积了厚度80nm的Si3N4薄膜,并利用紫外光刻和离子束刻蚀工艺将Si3N4制备成宽度为3.1μm的波导结构。随后,通过Si3N4带波导与倒锥形铌酸锂波导实现了高效耦合,耦合损耗低至0.75dB/facet。上述研究展现了异质集成技术在高效端面耦合和光子集成领域的巨大潜力。

楔形波导端面耦合器

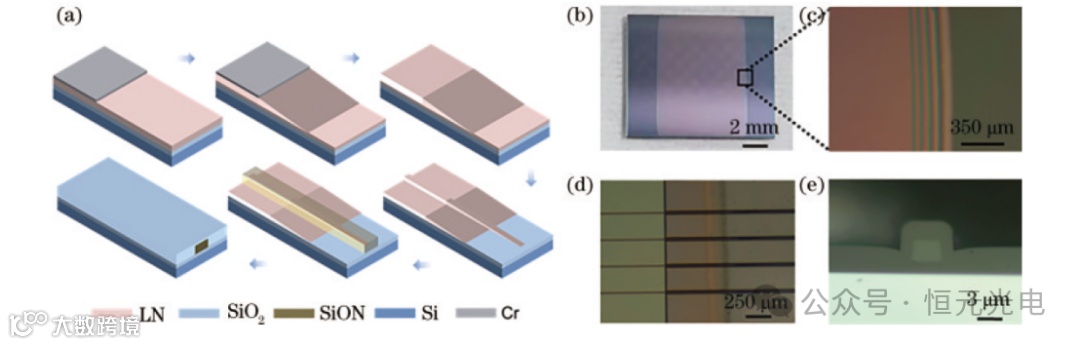

针对目前端面耦合器制备工艺难度大、耗时长、成本高等问题,该研究团队创新性地提出利用化学机械抛光工艺将铌酸锂波导宽度渐变转变为厚度渐变的方案,如图6(a)所示,该方案成功制备出了与紫外光刻技术兼容的铌酸锂端面耦合器结构,避免了使用窄波导和复杂的电子束光刻技术套刻过程。从图6(b)中可以看出,铌酸锂层的厚度呈楔形,楔形波导长度约为200μm,光信号首先从光纤耦合至氮氧化硅波导,然后通过氮氧化硅波导与单层铌酸锂楔形波导相互耦合,最终将光信号束缚至铌酸锂脊波导中。图6(c)与(d)分别给出了光由氮氧化硅束缚至铌酸锂波导过程中俯视和侧视的时域场分布。在图6(a)中对应端面耦合器横截面的结构及模场分布由图6(e)所示。

图 6 楔形波导端面耦合器基本设计。(a)端面耦合器整体结构示意图;(b)端面耦合器侧向截面图;氮氧化硅模式耦合至铌酸锂波导模式(c)俯视图和(d)侧视图时域场分布;(e)端面耦合器不同横截面处结构及对应的模式分布

图7(a)给出了端面耦合器详细制备步骤。首先在商用TFLN晶片(尺寸为1.2cm×1.0cm)上通过磁控溅射技术镀覆了400nm厚的铬膜,用作硬掩模。如图7(a)和(b)所示。之后,使用标准的晶圆抛光机,配合含有SiO2 颗粒的抛光悬浮液和柔软的天鹅绒抛光布,对铬掩模和暴露的TFLN进行化学机械抛光处理。如图7(c)所示,裸露的TFLN经抛磨后呈现出厚度缓变的楔形结构。

图7 晶圆片制备流程及局部显微镜图。(a)端面耦合器主要制备流程;(b)抛光后的晶圆片在(c)斜坡区域放大图像中存在高度差;(d)被氮氧化硅波导覆盖着的铌酸锂楔形波导区域;(e)端面处显微镜图像

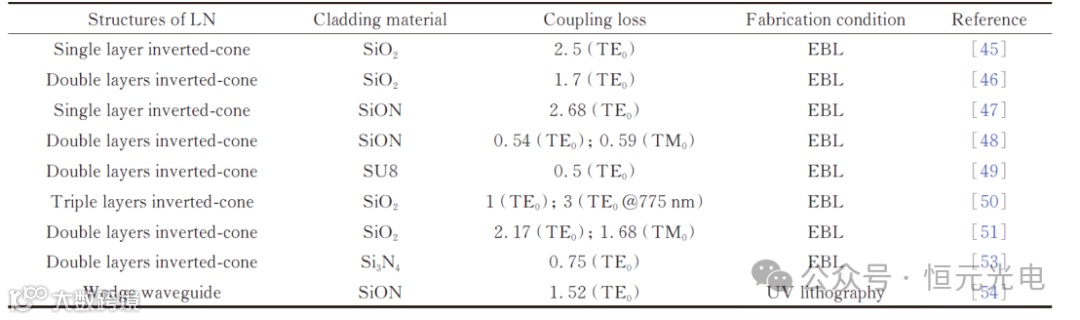

在进行后续加工前,使用刻铬液去除铬膜。通过电子束光刻和电感耦合等离子体-反应离子刻蚀(ICP-RIE)工艺制备铌酸锂波导。在端面耦合器斜坡处,铌酸锂厚度逐渐变化,宽度为600nm,可由i-line光刻技术替代电子束光刻,以降低制备成本。接着,通过PECVD、紫外光刻、离子束刻蚀技术在端面处制备出氮氧化硅波导。在氮氧化硅波导上再次通过PECVD 工艺沉积3μm厚的SiO2层,最后使用抛光机对芯片侧面进行精细研磨和抛光,如图7(d)和(e)所示。此项研究为大规模器件的制备及端面封装提供了一种高效、成本效益优良的解决方案。下表总结了TFLN平台端面耦合器的波导结构、包层材料、性能、制备条件等。

TFLN端面耦合器性能比较

总体来说,经过过去几年的研究,TFLN端面耦合器的研究取得了快速进步,随着引入了单层、多层倒锥形波导或者楔形波导等多种高效率的端面耦合器被成功设计和制备出来,TFLN芯片和光纤之间的损耗降低至1dB/facet以下。未来的研究将继续聚焦于提高耦合效率与带宽、通过实现小型化与集成化来增强波导与外部环境的交互能力。