然而,基于Voxel的方式采用的稀疏卷积算子Spconv一直面临着部署困难的问题,主要阻碍有两点,即低时延要求和与既有边缘设备推理引擎的适配。

前者的本质是如何实现一个高性能GEMM应用,而后者则需要将具有变长特性的Spconv与诸如TensorRT之类的定长推理引擎结合起来。

GEMM的优化

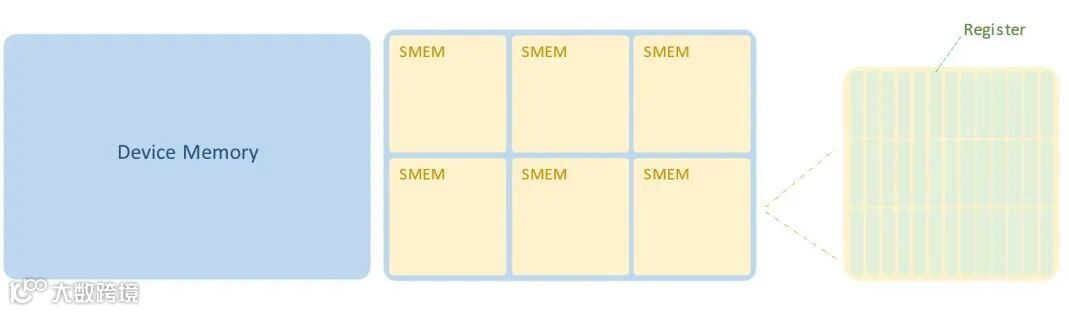

以NVIDIA的Ampere架构为例,每个Tensor Core负责实现一对16*16 与 16*8的半精度矩阵相乘,需要将这些数据从Global Memory读取到Shared Memory,再加载到寄存器中供Tensor Core计算,这个数据搬运过程可以借用CUTLASS中的Iterator概念来完成。

每个Iterator负责两种存储单元的数据通信,结合向量化访问,数据的搬运可以以最小开销完成。同时,因Tensor Core的运算与数据通信是异步进行的,还可以用Tensor Core来隐藏访存延迟。

而在Ampere架构中,只要Shared Memory的可用空间足够大,还可以使用不设上限的Buffer个数来实现更激进的延迟隐藏。

然而,每个Tensor Core只能计算特定规格的小矩阵,而在点云相关神经网络中往往需要处理拥有上百万浮点数的矩阵。在这种情况下,Tiling(分块)操作就必不可少。

Tiling的原理其实就是分治(Divide and Conquer), 将一个大矩阵划分成若干个小矩阵块,然后并行处理。

与TensorRT的结合部署

这套机制需要有两个基本特性。第一,对变长特性特别适配,能够灵活处理各种变长情况;第二,针对大显存需求的特别显存管理能力。

变长引擎与TensorRT的结合

至此,我们从两方面克服了Spconv的部署难点,并且将其运行速度与工作稳定性提升到了新高度。后续,这项工作依旧有不少拓展点,如高精度量化、全变长网络引擎的设计等。

觉非科技的真实场景实验

觉非科技用一组实验案例来比对下基于Spconv与基于Pillar和2D卷积的方法效果。

测试场景不同于一般的车端点云场景,而是路侧Lidar的感知情景。需要注意的是,因为安装高度与安装位姿的不同,路侧场景中平均每个交通参与者反射点数是车端场景的15%-50%。

示例场景中觉非框定了约1.5万平米的感知区域,包含了约2000平米的严重遮挡区域,平均每帧约100至150个感知目标,两颗固态Lidar投入使用。同时,由于路侧设备安装使点云拼接产生残影,这增加了对模型鲁棒性的考验。

觉非在实验中使用OpenPCDet中默认的Centerpoint-voxel与Centerpoint-pillar两个模型,视频为模型直出结果。

可以看到Pillar模型在道路中间处容易产生重叠识别,在下方过马路的目标中,有一辆小型三轮车在Pillar模型中也被频繁误检。而对右侧进入道路的大车识别的稳定性也不如Voxel模型。

通过使用专用引擎对稀疏卷积加速,觉非科技解决了Spconv算子的效率瓶颈与显存管理问题。利用稀疏卷积强大的性能,在众多业务场景的部署中,基于3D卷积的模型加快了算法的迭代周期,为开发人员提供了便利。

同时,凭借低时延与低显存占用,专用引擎加速的Spconv为其他系统节点节省了大量资源,也为整个自动驾驶系统贡献了鲁棒性与安全性,提升了整体系统的表现。

目前,基于城市与高速场景,通过路侧与车端的感知载体,觉非科技已进行了大量针对稀疏卷积的应用与迭代。

在不同实践情景下提炼的训练模型与实践经验,也反哺着觉非的算法不断升级。

1.SECOND: Sparsely Embedded Convolutional Detection

2.https://github.com/NVIDIA/cutlass

直播预告

觉非科技BEV感知的技术实践与迭代路径

觉非技术解析 | 激光雷达与视觉融合感知在自动驾驶中的应用

觉非科技:多传感器融合赋能智能驾驶量产落地