撰稿|由课题组供稿

近日,复旦大学微电子学院包文中课题组及其合作者,基于有实用化价值的4英寸单层MoS2晶圆,成功实现了低功率互补传输晶体管逻辑(CPL)电路结构。CPL结构属于传输管逻辑的一种,它由互补输入/输出、NMOS传输晶体管逻辑网络和输出反相器组成,可以在单极性晶体管的基础上优化电路面积并兼具CMOS的低功耗优势。该工作基于顶栅结构的二维MoS2场效应晶体管,对阈值电压和载流子迁移率等关键器件参数进行了协同优化。首先制造并测试了基本的反相器、静态随机存取存储器和环形振荡器,验证了二维电路集成工艺的可靠性。然后设计并实现了基于CPL结构的功能逻辑单元(AND/NAND、OR/NOR、XOR/XNOR、1位全加器),还进一步制备了CPL架构的数据选择器(MUX)、多路分解器(DEMUX)和左右移位器(SHIFTER)。这项工作展示了二维材料在集成电路中的实用化价值,并展示了复杂二维电路设计的潜力。

文章以“Pass-transistor Logic Circuits Based on Wafer-Scale Two-Dimensional Semiconductors”为题发表在期刊Advanced Materials上。复旦大学微电子学院硕博生王馨雨、陈新宇、马静怡为第一作者,复旦大学包文中研究员为该系列工作的主要通讯作者,复旦大学微电子学院包文中研究员、解玉风教授,以及复旦大学芯片与系统前沿技术研究院边历峰研究员为共同通讯作者。该工作得到了科技部重点研发计划纳米前沿专项、国家自然科学基金,上海市科委以及张江复旦国际创新中心集成电路创新平台的支持。

随着集成电路的制造工艺逐渐达到了硅材料本身的物理极限,新型二维原子晶体材料(简称二维材料),例如二硫化钼(MoS2)和二硫化钨(WS2)等硫族化合物,基于其具原子级别厚度、表面天然钝化、能够与标准半导体工艺兼容的优势,2020年开始,半导体主要玩家台积电、英特尔、三星以及创新技术策源欧洲地欧洲微电子研究中心IMEC,都已经大力布局二维材应用的二维材料研究成果并将其列为未来1纳米节点后晶体管技术的最重要方案。

近年来,二维材料的研究重点开始从基础研究逐渐向工程实际应用转移。大面积的材料生长也获得了突破,然而基于二维材料体的集成电路发展仍处于起步阶段,如何针对二维材料进行器件工艺和电路设计的定制优化是目前面临的主要。此外,由于二维硫族化合物中存在硫属元素空位,通常表现出N型半导体特性,目前为止报道的二维材料电路也主要基于典型的伪NMOS结构,与互补型的CMOS技术相比,伪NMOS集成电路有对晶体管均一性要求高、功耗较高等缺点。所以亟需寻找一种适合二维材料的电路架构。

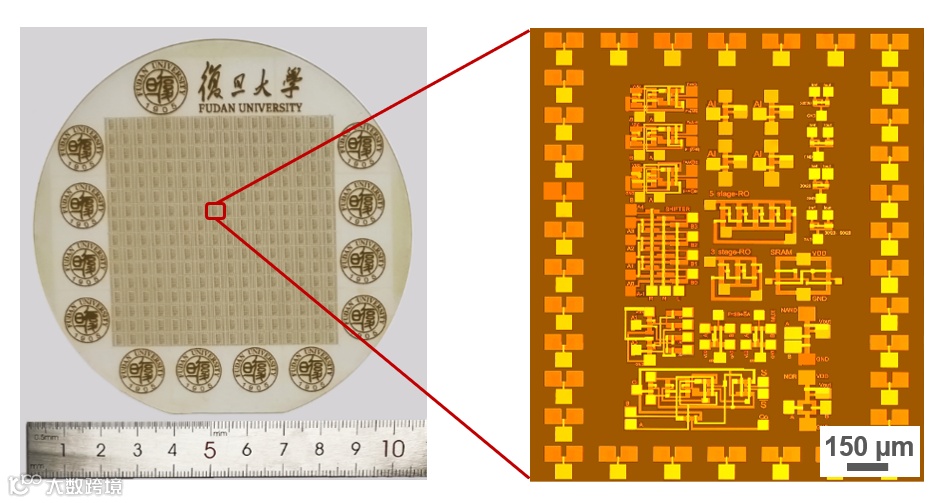

图1、制作有集成电路的4-inch MoS2晶圆的照片以及相应功能电路的光学显微镜图像。

首先,课题组和复旦孙正宗教授团队以及六碳科技合作研发,利用改进的CVD方法合成了单原子层、均匀性和可重复性好的4英寸MoS2薄膜,然后在4英寸MoS2晶圆上设计了256个区域,每个单元区域包含不同的功能电路和周围一圈用于基本测试的晶体管阵列,如图1所示。在此工作中,晶体管的结构并没有采用常规科研的“预埋底栅电极—转移二维材料”的方式,而是采用顶栅结构,直接在MoS2晶圆上进行中道和后道工艺,这与传统半导体制造工艺更为兼容。不过顶栅结构工艺更为复杂,因为原子级厚度的二维材料对其表面上层的工艺处理非常敏感。得益于课题组之前的工作积累,优化后的MoS2顶栅晶体管表现出了较好的增强型NMOS性能,有相对较低的亚阈值摆幅和高达108的电流开关比,并且在大面积上具有很好的均一性。

图2、基于MoS2的基本电路单元。(a) 反相器的横截面示意图; (b) 负载和驱动FET的对数转换特性;(c) 反相器的双稳态电压传输特性;(d) SRAM电路单元;(e) 3级环形振荡器;(f) SRAM的测试结果;(g) VDD = 3 V时3级环振的测试结果。

有了这些基础,研究团队制作了基于顶栅结构的电路单元,包括由不同材料顶栅构成的反相器(图2a-c),SRAM单元电路(图2d、f)和3级环形振荡器(图2e、g)。反相器电路中,栅极的优化可以让晶体管具有相同的宽长比,反相器的VM为0.8 V ,电压增益高达39。此外,优化后低输入信号电平(NML)和高输入信号电平(NMH)的噪声容限表明该反相器具有较好的抗噪能力。在高性能反相器的基础上,可以得到由两个交叉耦合到存储节点的反相器组成的触发器SRAM单元。这个SRAM单元有两个稳定的输出状态(0 V和3 V,VDD = 3 V),在30 s和90 s时,输入信号导通,而输出保持在状态 0 V 和 3 V(图2f),这证明稳定存储单元的作用。然后,还制造了基于反相器的环形振荡器(Ring Oscillator),这是一种传统的电路架构,通常用作脉冲或连续波可调谐源,如图2g所示,RO表现出稳定和自持的输出电压,在VDD = 3 V时可以实现53.7kHz的稳定振荡频率。由于研究条件所限,此工作中晶体管的特征尺寸较大,所以电路的速度和功耗并没有优势,但是当未来采用先进制程缩小沟道尺寸后,二维材料的性能优势将得到充分的释放。

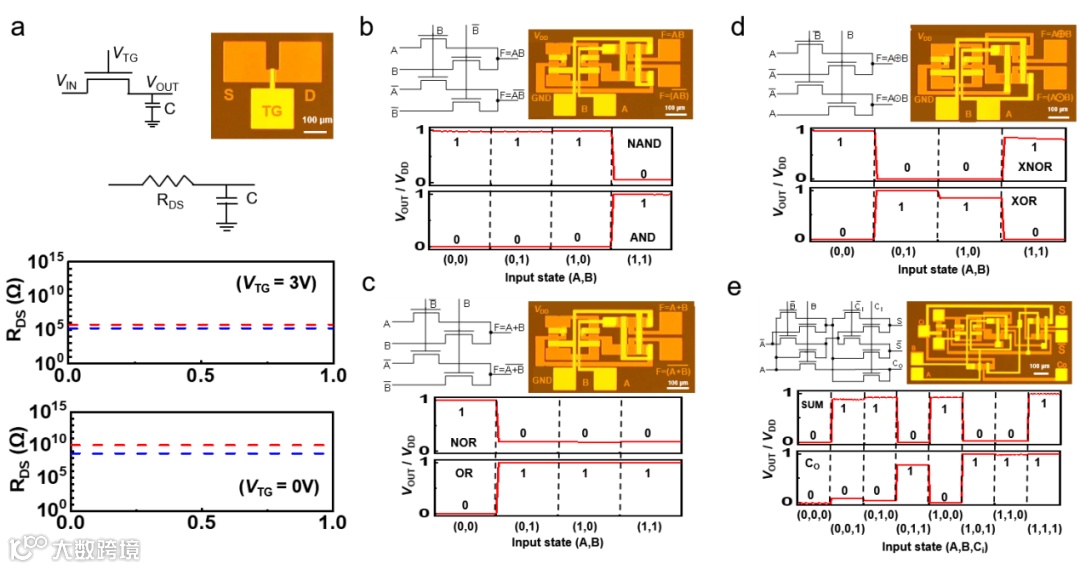

图3、基于 MoS2 的 CPL 电路。(a) CPL 电路的工作原理图;(b-e) 基于CPL结构的 NAND/AND (b)、NOR/OR (c)、XNOR/XOR (d) 和1位全加器(e)的电路示意图、光学显微镜图像和相应的逻辑功能测试结果。

随后,研究团队进一步将N型MoS2晶体管的特点和CPL结构结合,研究了基本的传输管逻辑电路单元。图 3a 展示了N型传输管的基本工作原理,当向VTG施加高电压(逻辑“1”)时,MoS2 传输晶体管的源极(输入)和漏极(输出)之间的电阻 (RDS) 约为105Ω或更小,这时处于“低阻”或“导通”状态,因此输入信号 (VIN) 可以从源极传递到漏极;当向栅极施加零电压(逻辑“0”)时,RDS大于108 Ω,此时传输晶体管处于“高阻”或“关闭”状态,VIN 信号无法传递到输出端。通过这个简单的传输管原理,基于CPL结构的AND/NAND、OR/NOR 、 XOR/XNOR、1位全加器都表现出精确的逻辑功能(图3b-e)。

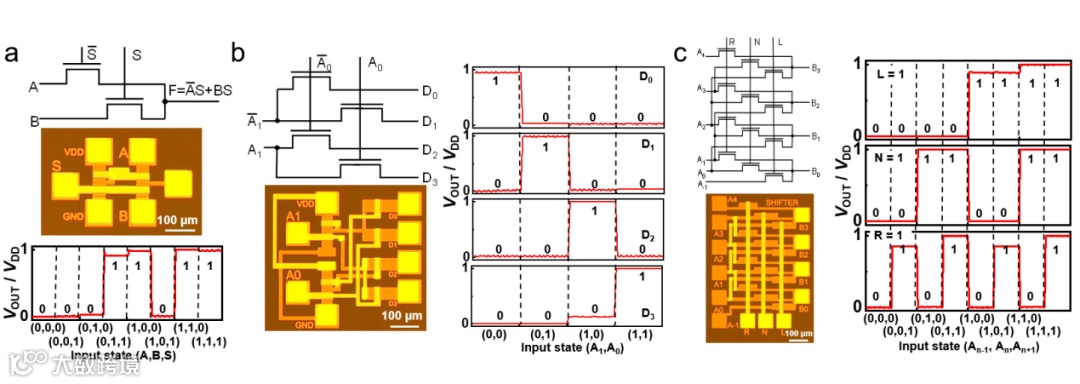

图4、 基于CPL结构的复杂MoS2功能电路。(a) 二选一 MUX电路; (b) 二到四通道 的DEMUX 电路;(c) 可控左右移位器(SHIFTER)的电路。

最后,研究团队还制作了更为复杂的CPL结构电路,如图4所示,包括MUX、DEMUX 和SHIFER这些是数字 IC中存储和逻辑处理电路中的关键组件。图4a是二选一 MUX 的电路示意图、光学显微图像和相应的功能测试结果,其中 S 是输入控制信号,当 S = 0 时,选择 A 信号作为输出, S = 1时,选择 B 信号作为输出。图4b展示了二到四通道 DEMUX的结果,它与 MUX 相反,四个输出(D0 到 D3)由 (A0, A1) 的不同组合选择。而移位器是一个复杂的多路开关电路,如图4c所示的可控左右移位器(SHIFTER)中,可以观察到在不同的控制信号(R、N、L)下,输出信号向左、向右移动或者保持不变。

本文系统地研究了二维半导体在集成电路方面的应用,利用有实用化价值的4-inch高质量单层MoS2薄膜成功制造了顶栅晶体管和有实用价值的复杂功能性电路。该研究工作不仅为未来电子器件的发展提供了一个新思路,也探索了二维材料在集成电路产业中的实用化价值。研究团队未来将继续聚焦于新型二维半导体,进一步推动其在半导体产业中的实际工程应用。

文献信息:

Pass-transistor Logic Circuits Based on Wafer-Scale Two-Dimensional Semiconductors

文献链接:

https://onlinelibrary.wiley.com/doi/10.1002/adma.202202472

包文中研究员课题组长期招收物理、微电子、材料、化学等专业的优秀本科生、硕博研究生,并提供薪酬具有竞争力的博士后岗位,详情可查看课题组网站的招聘信息https://2dlab.fudan.edu.cn/

免责声明:本文旨在传递更多科研资讯及分享,所有其他媒、网来源均注明出处,如涉及版权问题,请作者第一时间后台联系,我们将协调进行处理,所有来稿文责自负,两江仅作分享平台。转载请注明出处,如原创内容转载需授权,请联系下方微信号。